SN65LBC176A-EP Datasheet Summary

ąą

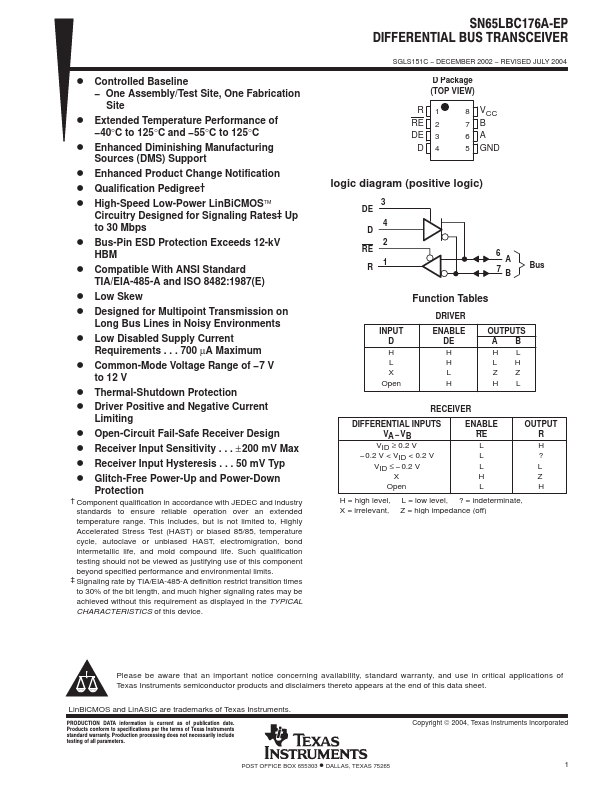

D Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

D Extended Temperature Performance of

- 40°C to 125°C and

- 55°C to 125°C

D Enhanced Diminishing Manufacturing

Sources (DMS) Support

D Enhanced Product Change Notification D Qualification Pedigree† D High-Speed Low-Power LinBiCMOS

Circuitry Designed for Signaling Rates‡ Up to 30 Mbps

D Bus-Pin ESD Protection Exceeds 12-kV

HBM

D patible With ANSI Standard

TIA/EIA-485-A and ISO 8482:1987(E)

D Low Skew D Designed for Multipoint Transmission on

Long Bus Lines in Noisy Environments

D Low Disabled Supply Current

Requirements . . . 700 µA Maximum

D mon-Mode Voltage Range of

- 7 V to 12 V

D Thermal-Shutdown Protection D Driver Positive and Negative Current

Limiting

D Open-Circuit Fail-Safe Receiver Design D Receiver Input Sensitivity . . . ± 200 mV Max D Receiver Input Hysteresis . . . 50 mV Typ D Glitch-Free Power-Up and Power-Down

Protection

† ponent qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold pound life. Such qualification testing should not be viewed as justifying use of this ponent beyond specified performance and environmental limits.

‡ Signaling rate by TIA/EIA-485-A definition restrict transition times to 30% of the bit length, and much higher signaling rates may be achieved without this requirement as displayed in the TYPICAL CHARACTERISTICS of this device.

SN65LBC176AĆEP DIFFERENTIAL BUS TRANSCEIVER

ą

SGLS151C

- DECEMBER...