SN65LVDS32

SN65LVDS32 is High-Speed Differential Line Receivers manufactured by Texas Instruments.

Product Folder

Sample & Buy

Technical Documents

Tools & Software

Support & munity

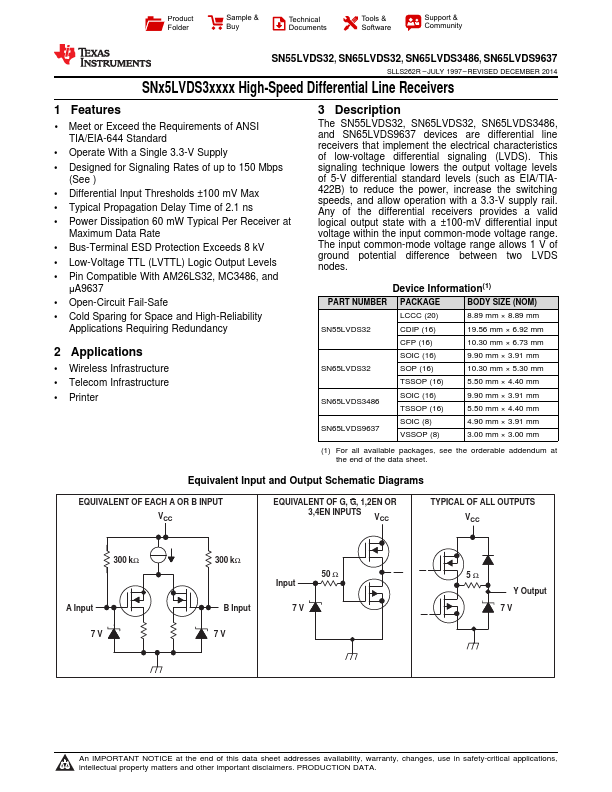

SN55LVDS32, SN65LVDS32, SN65LVDS3486, SN65LVDS9637

SLLS262R

- JULY 1997

- REVISED DECEMBER 2014

SNx5LVDS3xxxx High-Speed Differential Line Receivers

1 Features

- 1 Meet or Exceed the Requirements of ANSI TIA/EIA-644 Standard

- Operate With a Single 3.3-V Supply

- Designed for Signaling Rates of up to 150 Mbps

(See )

- Differential Input Thresholds ±100 mV Max

- Typical Propagation Delay Time of 2.1 ns

- Power Dissipation 60 mW Typical Per Receiver at

Maximum Data Rate

- Bus-Terminal ESD Protection Exceeds 8 kV

- Low-Voltage TTL (LVTTL) Logic Output Levels

- Pin patible With AM26LS32, MC3486,...