SN65LVDT388A Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 38

Operating Voltage: 3.3 V

Description

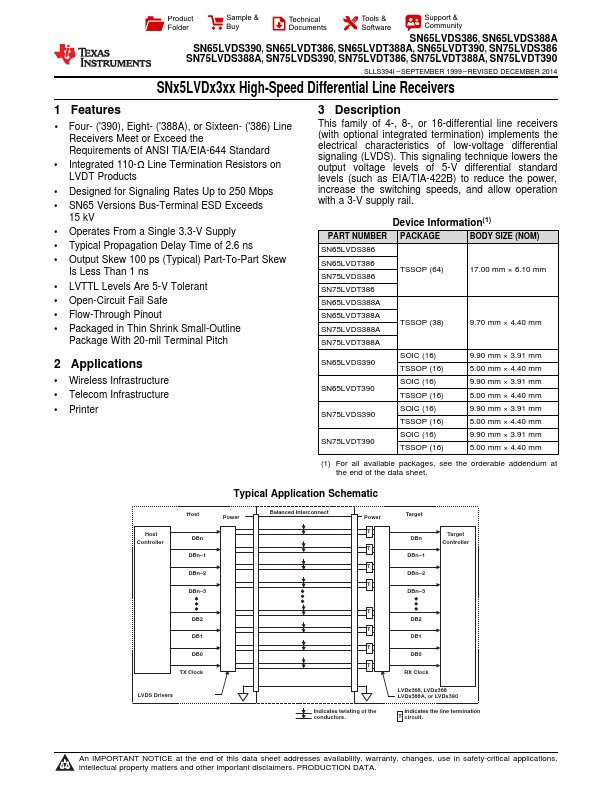

This family of 4-, 8-, or 16-differential line receivers (with optional integrated termination) implements the Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) SN65LVDS386 SN65LVDT386 SN75LVDS386 TSSOP (64) 17.00 mm × 6.10 mm SN75LVDT386 SN65LVDS388A SN65LVDT388A SN75LVDS388A TSSOP (38) 9.70 mm × 4.40 mm SN75LVDT388A SN65LVDS390 SOIC (16) TSSOP (16) 9.90 mm × 3.91 mm 5.00 mm × 4.40 mm SN65LVDT390 SOIC (16) TSSOP (16) 9.90 mm × 3.91 mm 5.00 mm × 4.40 mm SN75LVDS390 SOIC (16) TSSOP (16) 9.90 mm × 3.91 mm 5.00 mm × 4.40 mm SN75LVDT390 SOIC (16) TSSOP (16) 9.90 mm × 3.91 mm 5.00 mm × 4.40 mm (.

Key Features

- 1 Four- ('390), Eight- ('388A), or Sixteen- ('386) Line Receivers Meet or Exceed the Requirements of ANSI TIA/EIA-644 Standard

- Integrated 110-Ω Line Termination Resistors on LVDT Products

- Designed for Signaling Rates Up to 250 Mbps

- SN65 Versions Bus-Terminal ESD Exceeds 15 kV

- Operates From a Single 3.3-V Supply