Datasheet Summary

D State-of-the-Art EPIC-ΙΙB™ BiCMOS Design

Significantly Reduces Power Dissipation

D ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R = 0)

D Latch-Up Performance Exceeds 500 mA Per

JEDEC Standard JESD-17

D Typical VOLP (Output Ground Bounce) < 1 V at VCC = 5 V, TA = 25°C

D High-Drive Outputs (- 32-mA IOH,

64-mA IOL )

D Parity Error Flag With Parity

Generator/Checker

D Register for Storage of the Parity Error Flag D Package Options Include Plastic

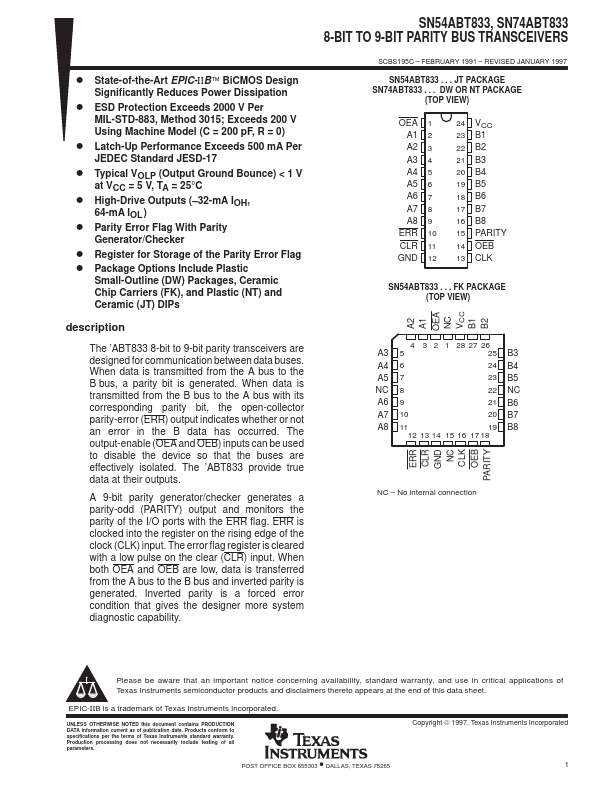

Small-Outline (DW) Packages, Ceramic Chip Carriers (FK), and Plastic (NT) and Ceramic (JT) DIPs description

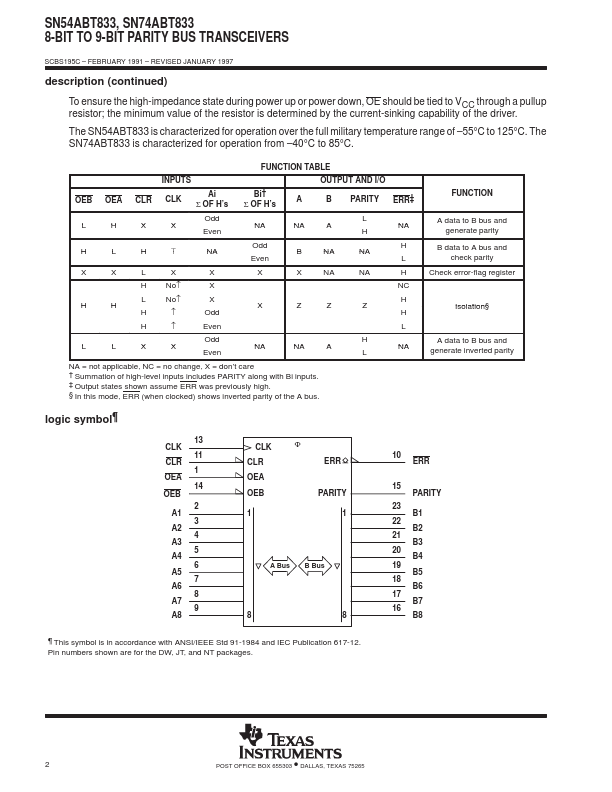

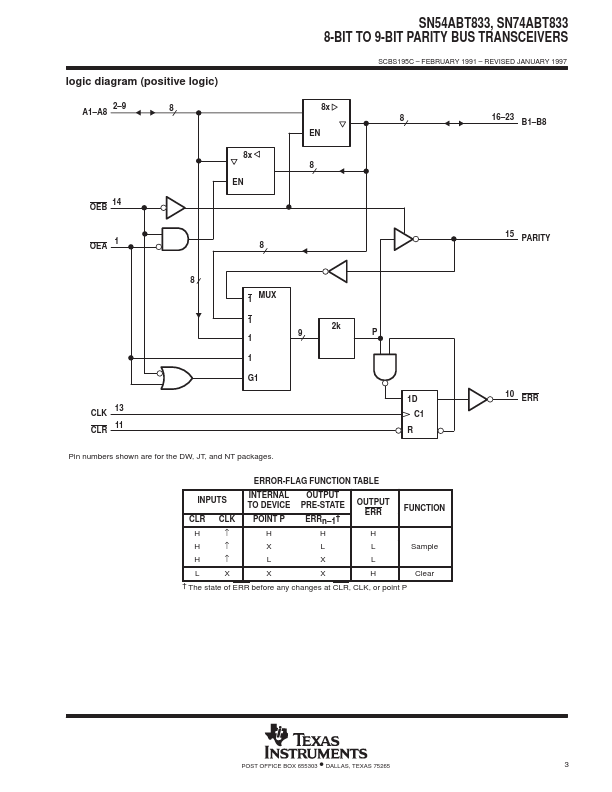

The ’ABT833 8-bit to 9-bit parity transceivers are designed for munication...