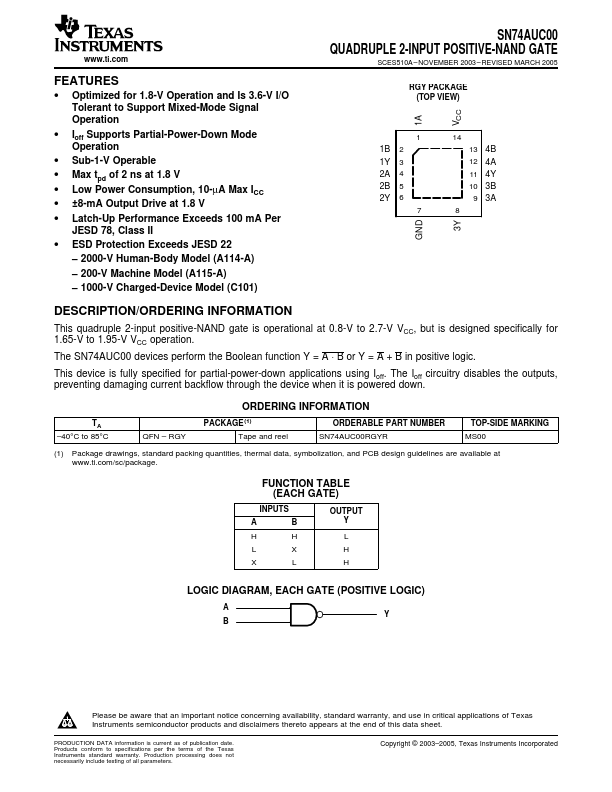

SN74AUC00

Overview

- Optimized for 1.8-V Operation and Is 3.6-V I/O Tolerant to Support Mixed-Mode Signal Operation

- Ioff Supports Partial-Power-Down Mode Operation

- Sub-1-V Operable

- Max tpd of 2 ns at 1.8 V

- Low Power Consumption, 10-µA Max ICC

- ±8-mA Output Drive at 1.8 V

- Latch-Up Performance Exceeds 100 mA Per