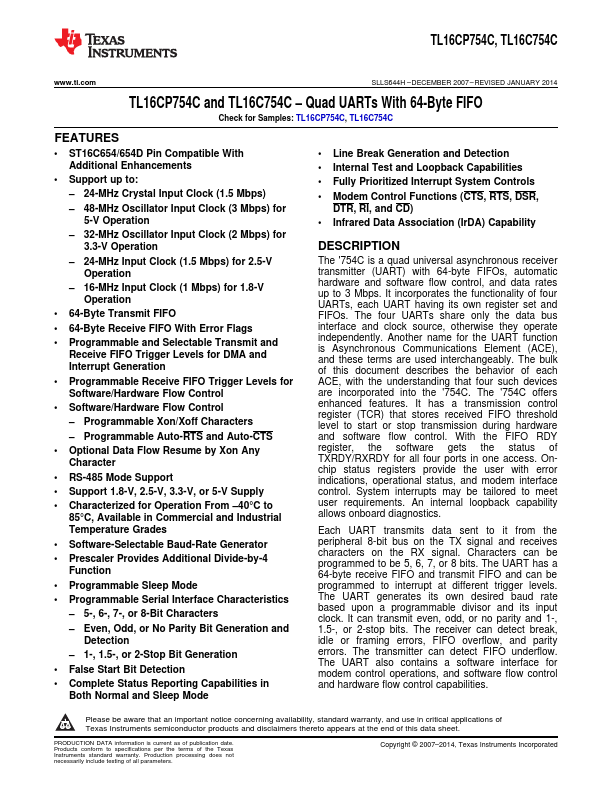

TL16CP754CI

Overview

The '754C is a quad universal asynchronous receiver transmitter (UART) with 64-byte FIFOs, automatic hardware and software flow control, and data rates up to 3 Mbps.

- ST16C654/654D Pin Compatible With Additional Enhancements

- Support up to: - 24-MHz Crystal Input Clock (1.5 Mbps) - 48-MHz Oscillator Input Clock (3 Mbps) for 5-V Operation - 32-MHz Oscillator Input Clock (2 Mbps) for 3.3-V Operation - 24-MHz Input Clock (1.5 Mbps) for 2.5-V Operation - 16-MHz Input Clock (1 Mbps) for 1.8-V Operation

- 64-Byte Transmit FIFO

- 64-Byte Receive FIFO With Error Flags

- Programmable and Selectable Transmit and Receive FIFO Trigger Levels for DMA and Interrupt Generation

- Programmable Receive FIFO Trigger Levels for Software/Hardware Flow Control

- Software/Hardware Flow Control - Programmable Xon/Xoff Characters - Programmable Auto-RTS and Auto-CTS

- Optional Data Flow Resume by Xon Any Character

- RS-485 Mode Support

- Support 1.8-V, 2.5-V, 3.3-V, or 5-V Supply