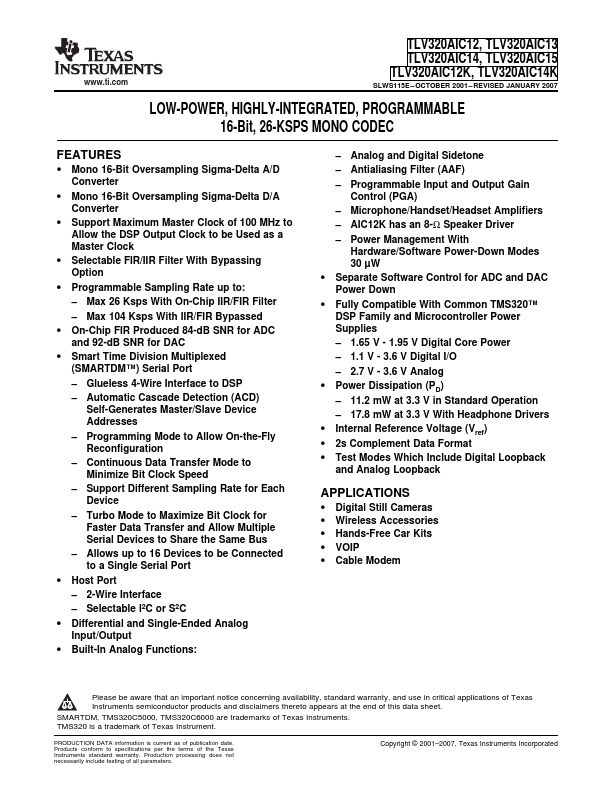

TLV320AIC13

Description

The TLV320AIC1x is a true low-cost, low-power, high-integrated, high-performance, mono voice codec. It features one 16-bit analog-to-digital (A/D) channel and one 16-bit digital-to-analog (D/A) channel.

Key Features

- Mono 16-Bit Oversampling Sigma-Delta A/D Converter

- Mono 16-Bit Oversampling Sigma-Delta D/A Converter

- Support Maximum Master Clock of 100 MHz to Allow the DSP Output Clock to be Used as a Master Clock

- Selectable FIR/IIR Filter With Bypassing Option

- Programmable Sampling Rate up to: – Max 26 Ksps With On-Chip IIR/FIR Filter – Max 104 Ksps With IIR/FIR Bypassed

- On-Chip FIR Produced 84-dB SNR for ADC and 92-dB SNR for DAC

- Host Port – 2-Wire Interface – Selectable I2C or S2C

- Differential and Single-Ended Analog Input/Output

- Separate Software Control for ADC and DAC Power Down

- Fully compatible With mon TMS320™ DSP Family and Microcontroller Power Supplies – 1.65 V