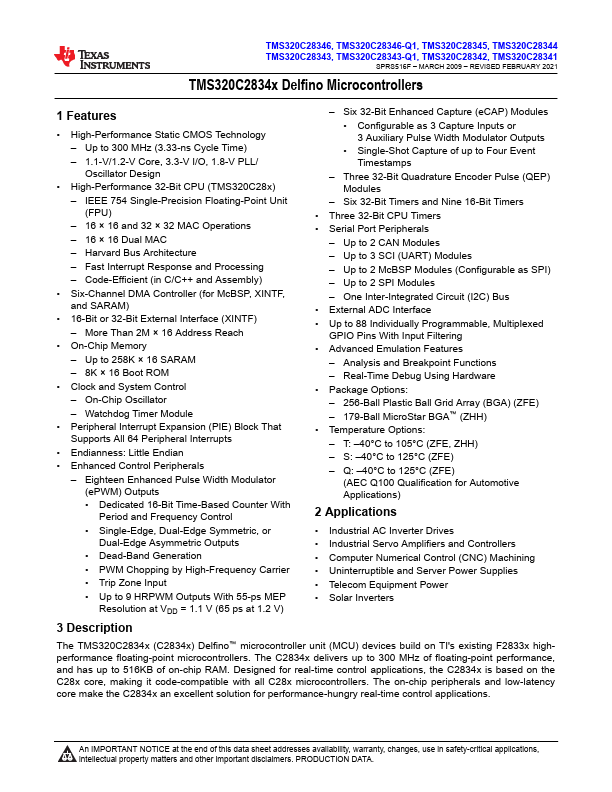

TMS320C28345

Key Features

- High-Performance Static CMOS Technology - Up to 300 MHz (3.33-ns Cycle Time) - 1.1-V/1.2-V Core, 3.3-V I/O, 1.8-V PLL/ Oscillator Design

- High-Performance 32-Bit CPU (TMS320C28x) - IEEE 754 Single-Precision Floating-Point Unit (FPU) - 16 × 16 and 32 × 32 MAC Operations - 16 × 16 Dual MAC - Harvard Bus Architecture - Fast Interrupt Response and Processing - Code-Efficient (in C/C++ and Assembly)

- Six-Channel DMA Controller (for McBSP, XINTF, and SARAM)

- 16-Bit or 32-Bit External Interface (XINTF) - More Than 2M × 16 Address Reach

- On-Chip Memory - Up to 258K × 16 SARAM - 8K × 16 Boot ROM

- Clock and System Control - On-Chip Oscillator - Watchdog Timer Module

- Peripheral Interrupt Expansion (PIE) Block That Supports All 64 Peripheral Interrupts

- Endianness: Little Endian

- Enhanced Control Peripherals - Eighteen Enhanced Pulse Width Modulator (ePWM) Outputs

- Dedicated 16-Bit Time-Based Counter With Period and Frequency Control