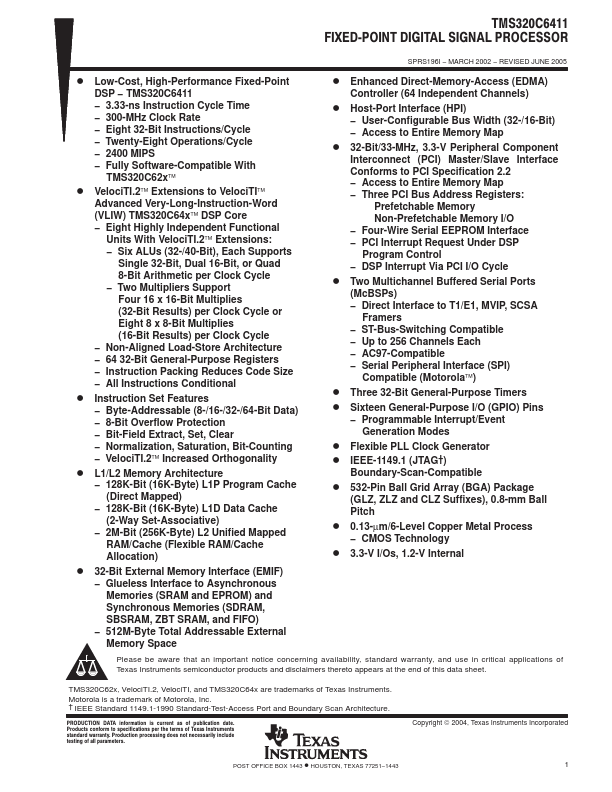

TMS320C6411

Key Features

- 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped)

- 2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation) D 32-Bit External Memory Interface (EMIF)

- Glueless Interface to Asynchronous Memories (SRAM and EPROM) and Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO)