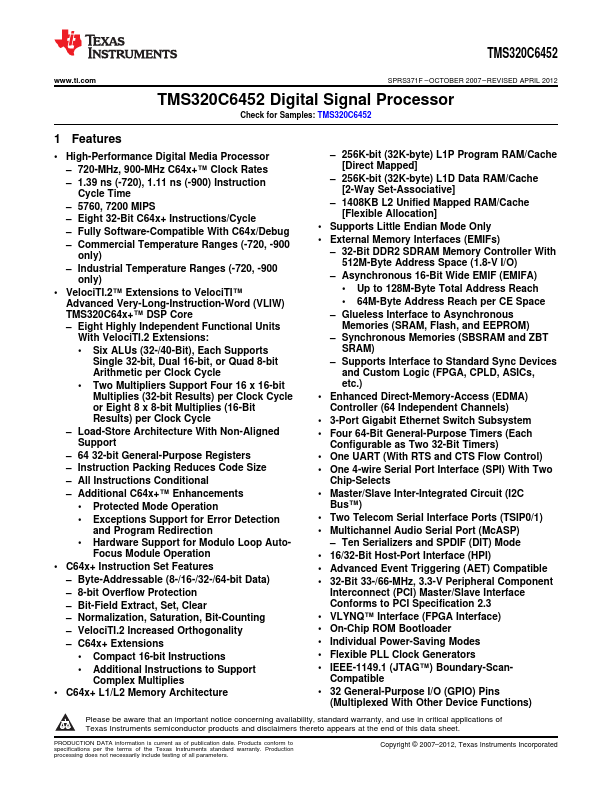

TMS320C6452 Overview

Key Specifications

Package: FCBGA

Pins: 529

Max Frequency: 900 MHz

Height: 3.3 mm

Key Features

- Supports Little Endian Mode Only

- Up to 128M-Byte Total Address Reach

- Two Multipliers Support Four 16 x 16-bit etc.) Multiplies (32-bit Results) per Clock Cycle

- Enhanced Direct-Memory-Access (EDMA) or Eight 8 x 8-bit Multiplies (16-Bit Controller (64 Independent Channels) Results) per Clock Cycle

- 3-Port Gigabit Ethernet Switch Subsystem – Load-Store Architecture With Non-Aligned Support