TMS320C6674

Key Features

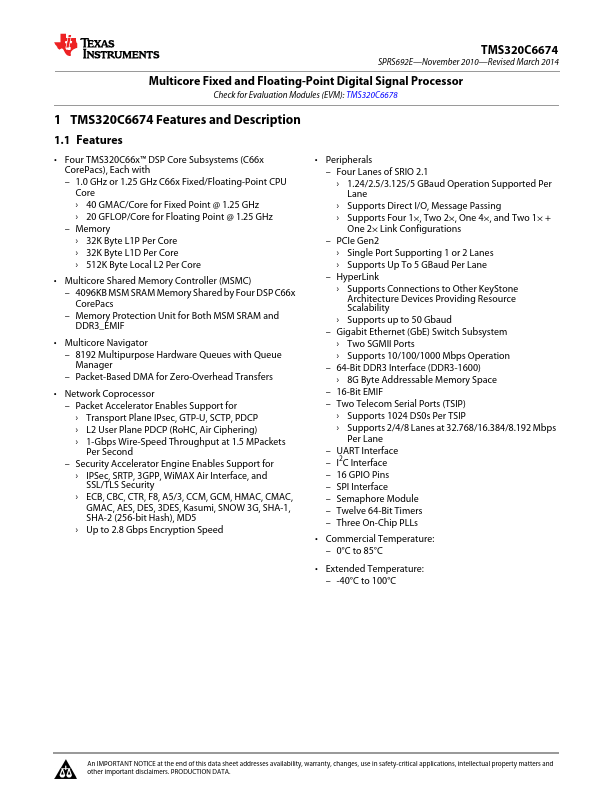

- 1 Features

- Four TMS320C66x™ DSP Core Subsystems (C66x CorePacs), Each with - 1.0 GHz or 1.25 GHz C66x Fixed/Floating-Point CPU Core › 40 GMAC/Core for Fixed Point @ 1.25 GHz › 20 GFLOP/Core for Floating Point @ 1.25 GHz - Memory › 32K Byte L1P Per Core › 32K Byte L1D Per Core › 512K Byte Local L2 Per Core

- Multicore Shared Memory Controller (MSMC) - 4096KB MSM SRAM Memory Shared by Four DSP C66x CorePacs - Memory Protection Unit for Both MSM SRAM and DDR3_EMIF

- Multicore Navigator - 8192 Multipurpose Hardware Queues with Queue Manager - Packet-Based DMA for Zero-Overhead Transfers

- Network Coprocessor - Packet Accelerator Enables Support for › Transport Plane IPsec, GTP-U, SCTP, PDCP › L2 User Plane PDCP (RoHC, Air Ciphering) › 1-Gbps Wire-Speed Throughput at 1.5 MPackets Per Second - Security Accelerator Engine Enables Support for › IPSec, SRTP, 3GPP, WiMAX Air Interface, and SSL/TLS Security › ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC, GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1, SHA-2 (256-bit Hash), MD5 › Up to 2.8 Gbps Encryption Speed

- Peripherals - Four Lanes of SRIO 2.1 › 1.24/2.5/3.125/5 GBaud Operation Supported Per Lane › Supports Direct I/O, Message Passing › Supports Four 1×, Two 2×, One 4×, and Two 1× + One 2× Link Configurations - PCIe Gen2 › Single Port Supporting 1 or 2 Lanes › Supports Up To 5 GBaud Per Lane - HyperLink › Supports Connections to Other KeyStone Architecture Devices Providing Resource Scalability › Supports up to 50 Gbaud - Gigabit Ethernet (GbE) Switch Subsystem › Two SGMII Ports › Supports 10/100/1000 Mbps Operation - 64-Bit DDR3 Interface (DDR3-1600) › 8G Byte Addressable Memory Space - 16-Bit EMIF - Two Telecom Serial Ports