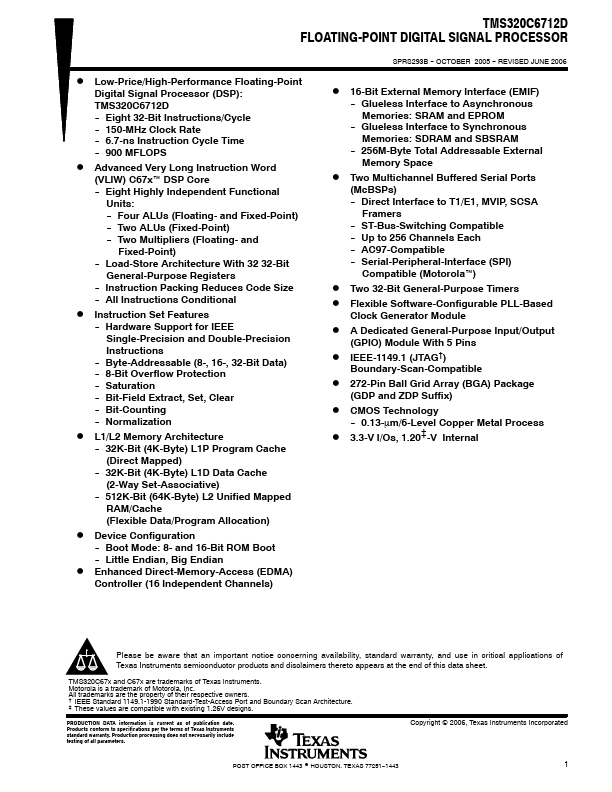

TMS320C6712D

Overview

- L1/L2 Memory Architecture -- 32K-Bit (4K-Byte) L1P Program Cache (Direct Mapped) -- 32K-Bit (4K-Byte) L1D Data Cache (2-Way Set-Associative) -- 512K-Bit (64K-Byte) L2 Unified Mapped RAM/Cache (Flexible Data/Program Allocation)

- Device Configuration -- Boot Mode: 8- and 16-Bit ROM Boot -- Little Endian, Big Endian

- Enhanced Direct-Memory-Access (EDMA) Controller (16 Independent Channels)