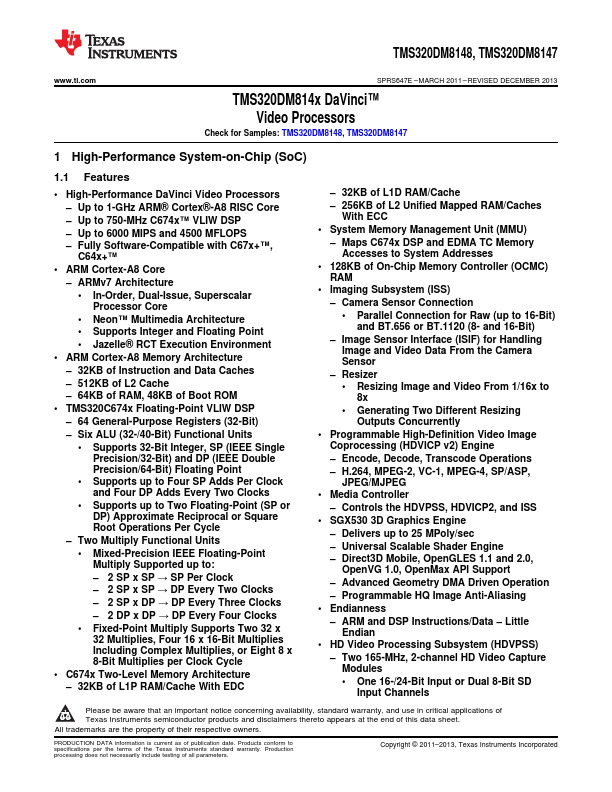

TMS320DM8148 Overview

Key Specifications

Package: FCBGA

Mount Type: Surface Mount

Pins: 684

Operating Voltage: 1.2 V

Key Features

- ARM Cortex-A8 Core – ARMv7 Architecture

- In-Order, Dual-Issue, Superscalar Processor Core

- Neon™ Multimedia Architecture

- Supports Integer and Floating Point

- Jazelle® RCT Execution Environment