TMS320F28030-Q1

Overview

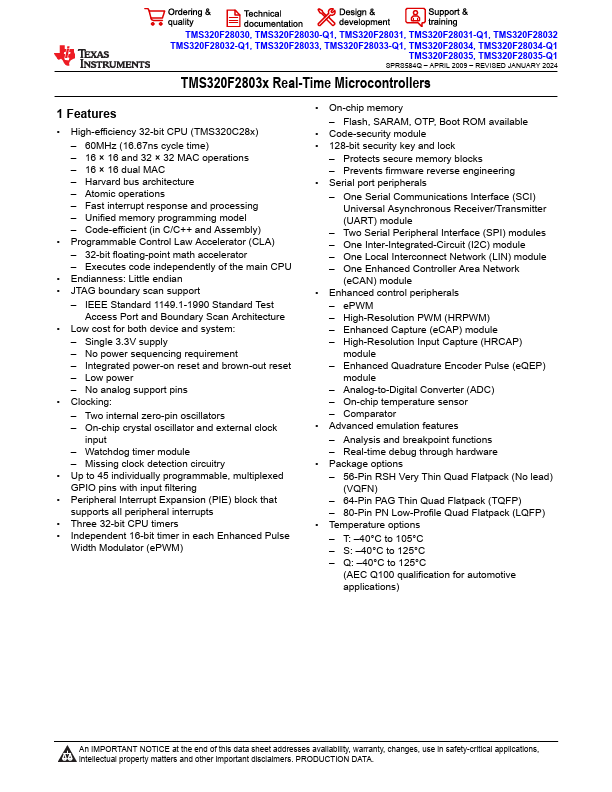

- High-efficiency 32-bit CPU (TMS320C28x) - 60MHz (16.67ns cycle time) - 16 × 16 and 32 × 32 MAC operations - 16 × 16 dual MAC - Harvard bus architecture - Atomic operations - Fast interrupt response and processing - Unified memory programming model - Code-efficient (in C/C++ and Assembly)

- Programmable Control Law Accelerator (CLA) - 32-bit floating-point math accelerator - Executes code independently of the main CPU

- Endianness: Little endian

- JTAG boundary scan support - IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- Low cost for both device and system: - Single 3.3V supply - No power sequencing requirement - Integrated power-on reset and brown-out reset - Low power - No analog support pins

- Clocking: - Two internal zero-pin oscillators - On-chip crystal oscillator and external clock input - Watchdog timer module - Missing clock detection circuitry

- Up to 45 individually programmable, multiplexed GPIO pins with input filtering

- Peripheral Interrupt Expansion (PIE) block that supports all peripheral interrupts

- Three 32-bit CPU timers

- Independent 16-bit timer in each Enhanced Pulse Width Modulator (ePWM)