TMS320F28031-Q1

TMS320F28031-Q1 is Microcontrollers manufactured by Texas Instruments.

- Part of the TMS320F28030 comparator family.

- Part of the TMS320F28030 comparator family.

TMS320F28030, TMS320F28030-Q1, TMS320F28031, TMS320F28031-Q1, TMS320F28032 TMS320F28032-Q1, TMS320F28033, TMS320F28033-Q1, TMS320F28034, TMS320F28034-Q1

TMS320F28035, TMS320F28035-Q1

SPRS584Q

- APRIL 2009

- REVISED JANUARY 2024

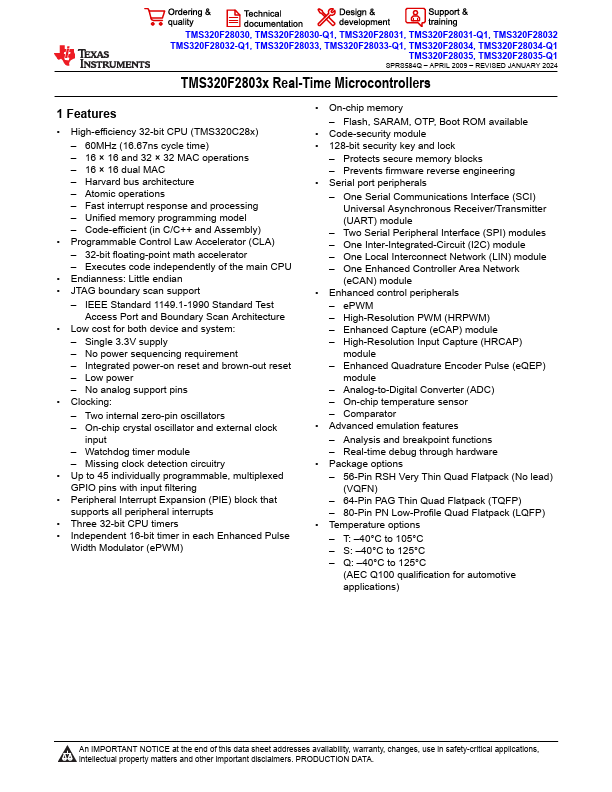

TMS320F2803x Real-Time Microcontrollers

1 Features

- High-efficiency 32-bit CPU (TMS320C28x)

- 60MHz (16.67ns cycle time)

- 16 × 16 and 32 × 32 MAC operations

- 16 × 16 dual MAC

- Harvard bus architecture

- Atomic operations

- Fast interrupt response and processing

- Unified memory programming model

- Code-efficient (in C/C++ and Assembly)

- Programmable Control Law Accelerator (CLA)

- 32-bit floating-point math accelerator

- Executes code independently of the main...