TMS320F28052

Overview

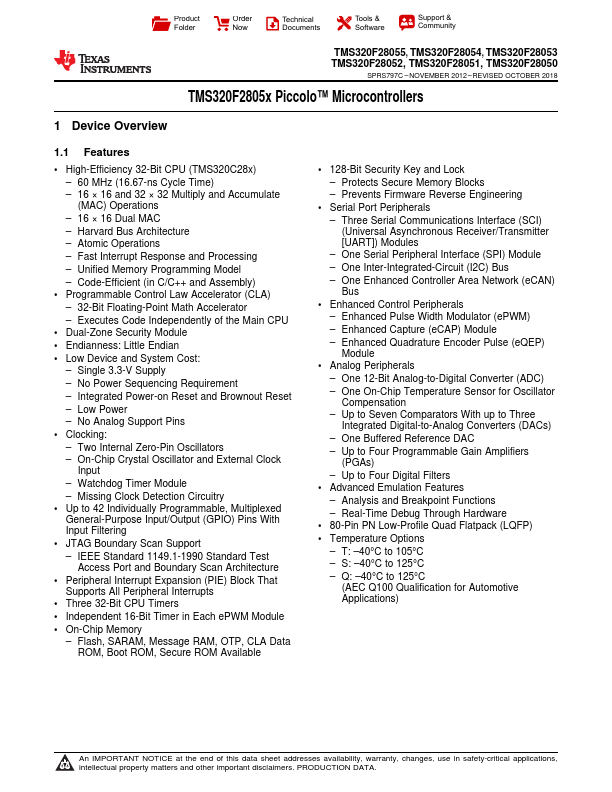

- High-Efficiency 32-Bit CPU (TMS320C28x) - 60 MHz (16.67-ns Cycle Time) - 16 × 16 and 32 × 32 Multiply and Accumulate (MAC) Operations - 16 × 16 Dual MAC - Harvard Bus Architecture - Atomic Operations - Fast Interrupt Response and Processing - Unified Memory Programming Model - Code-Efficient (in C/C++ and Assembly)

- Programmable Control Law Accelerator (CLA) - 32-Bit Floating-Point Math Accelerator - Executes Code Independently of the Main CPU

- Dual-Zone Security Module

- Endianness: Little Endian

- Low Device and System Cost: - Single 3.3-V Supply - No Power Sequencing Requirement - Integrated Power-on Reset and Brownout Reset - Low Power - No Analog Support Pins

- Clocking: - Two Internal Zero-Pin Oscillators - On-Chip Crystal Oscillator and External Clock Input - Watchdog Timer Module - Missing Clock Detection Circuitry

- Up to 42 Individually Programmable, Multiplexed General-Purpose Input/Output (GPIO) Pins With Input Filtering

- JTAG Boundary Scan Support - IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- Peripheral Interrupt Expansion (PIE) Block That Supports All Peripheral Interrupts

- Three 32-Bit CPU Timers