TMS320F28068 Overview

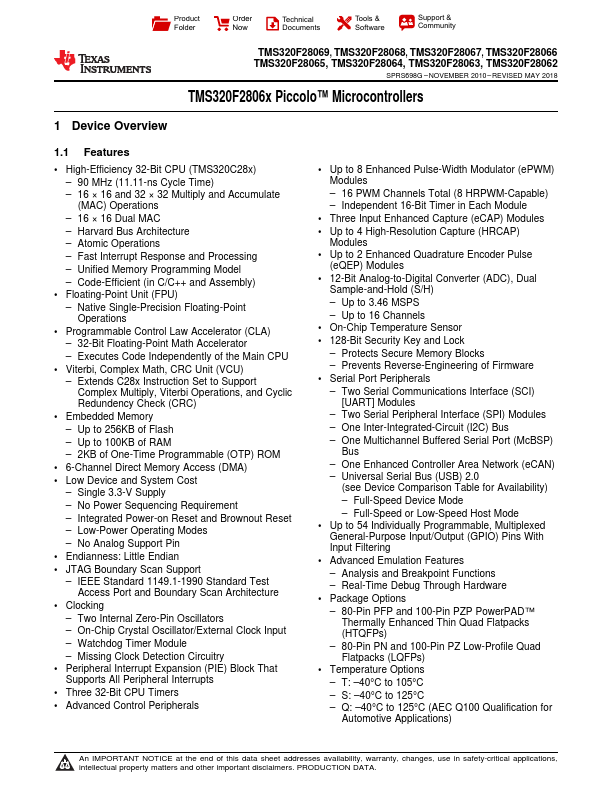

Key Features

- Floating-Point Unit (FPU) – Native Single-Precision Floating-Point Operations

- Programmable Control Law Accelerator (CLA) – 32-Bit Floating-Point Math Accelerator – Executes Code Independently of the Main CPU

- Embedded Memory – Up to 256KB of Flash – Up to 100KB of RAM – 2KB of One-Time Programmable (OTP) ROM

- 6-Channel Direct Memory Access (DMA)

- Endianness: Little Endian

- JTAG Boundary Scan Support – IEEE Standard 1149.1-1990 Standard Test Access Port and Boundary Scan Architecture

- Peripheral Interrupt Expansion (PIE) Block That Supports All Peripheral Interrupts

- Three 32-Bit CPU Timers

- Advanced Control Peripherals 1

- Up to 8 Enhanced Pulse-Width Modulator (ePWM) Modules – 16 PWM Channels Total (8 HRPWM-Capable) – Independent 16-Bit Timer in Each Module