TMS320F2811-Q1 Overview

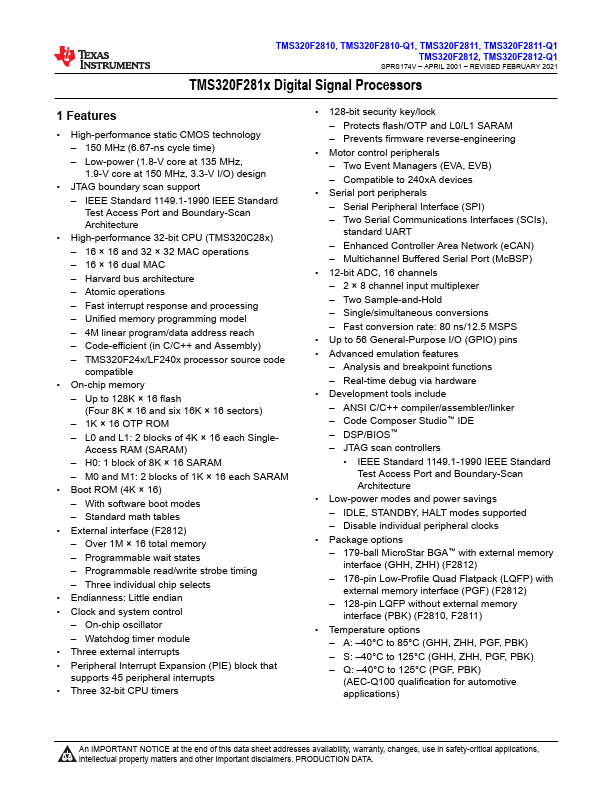

Key Features

- JTAG boundary scan support – IEEE Standard 1149.1-1990 IEEE Standard Test Access Port and Boundary-Scan Architecture

- Boot ROM (4K ×

- With software boot modes – Standard math tables

- Endianness: Little endian

- Clock and system control – On-chip oscillator – Watchdog timer module