TMS570LS20206-EP

Description

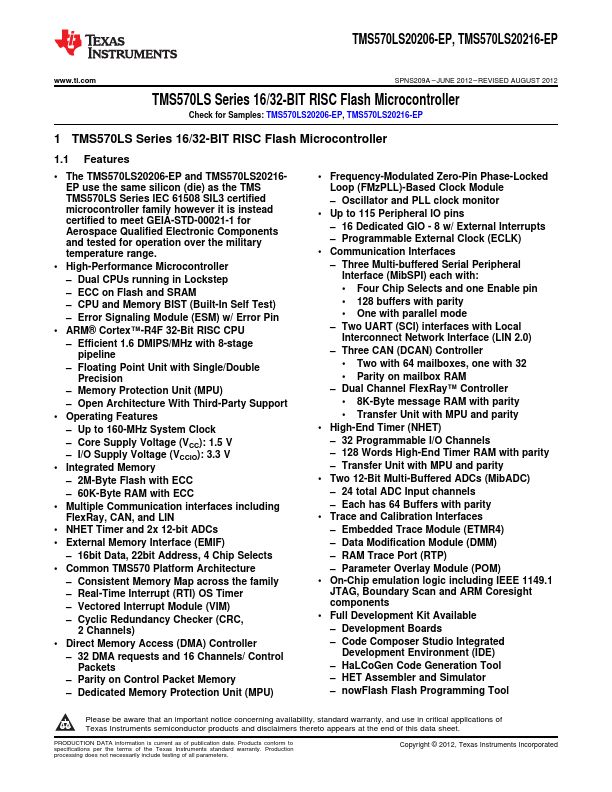

The TMS570LS series is a high performance microcontroller family. The architecture includes Dual CPUs in lockstep, CPU and Memory Built-In Self Test (BIST) logic, ECC on both the Flash and the data SRAM, parity on peripheral memories, and loop back capability on peripheral IOs.

Key Features

- The TMS570LS20206-EP and TMS570LS20216EP use the same silicon (die) as the TMS TMS570LS Series IEC 61508 SIL3 certified microcontroller family however it is instead certified to meet GEIA-STD-00021-1 for Aerospace Qualified Electronic Components and tested for operation over the military temperature range.

- High-Performance Microcontroller - Dual CPUs running in Lockstep - ECC on Flash and SRAM - CPU and Memory BIST (Built-In Self Test) - Error Signaling Module (ESM) w/ Error Pin

- ARM® Cortex™-R4F 32-Bit RISC CPU - Efficient 1.6 DMIPS/MHz with 8-stage pipeline - Floating Point Unit with Single/Double Precision - Memory Protection Unit (MPU) - Open Architecture With Third-Party Support

- Operating Features - Up to 160-MHz System Clock - Core Supply Voltage (VCC): 1.5 V - I/O Supply Voltage (VCCIO): 3.3 V

- Integrated Memory - 2M-Byte Flash with ECC - 60K-Byte RAM with ECC

- Multiple Communication interfaces including FlexRay, CAN, and LIN

- NHET Timer and 2x 12-bit ADCs

- External Memory Interface (EMIF) - 16bit Data, 22bit Address, 4 Chip Selects

- Common TMS570 Platform Architecture - Consistent Memory Map across the family - Real-Time Interrupt (RTI) OS Timer - Vectored Interrupt Module (VIM) - Cyclic Redundancy Checker (CRC, 2 Channels)

- Direct Memory Access (DMA) Controller - 32 DMA requests and 16 Channels/ Control Packets - Parity on Control Packet Memory - Dedicated Memory Protection Unit (MPU)