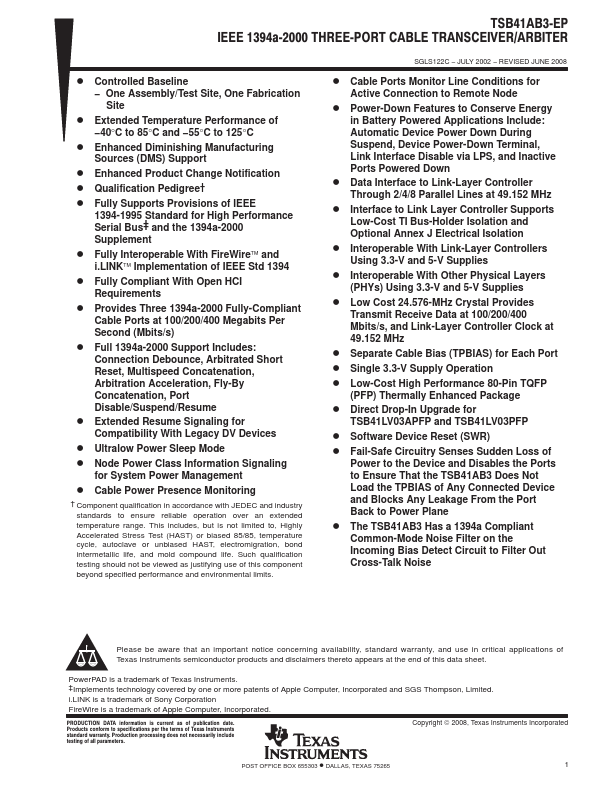

| Part | TSB41AB3-EP |

|---|---|

| Description | IEEE 1394a-2000 Three-Port Cable Transceiver/Arbiter |

| Manufacturer | Texas Instruments |

| Size | 941.47 KB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| MBL8289-1 | Fujitsu Semiconductor Limited | BIPOLAR BUS ARBITER |

| 82C89 | Intersil | CMOS Bus Arbiter |

| MD82C89 | Intersil | CMOS Bus Arbiter |