74AHC574PW Description

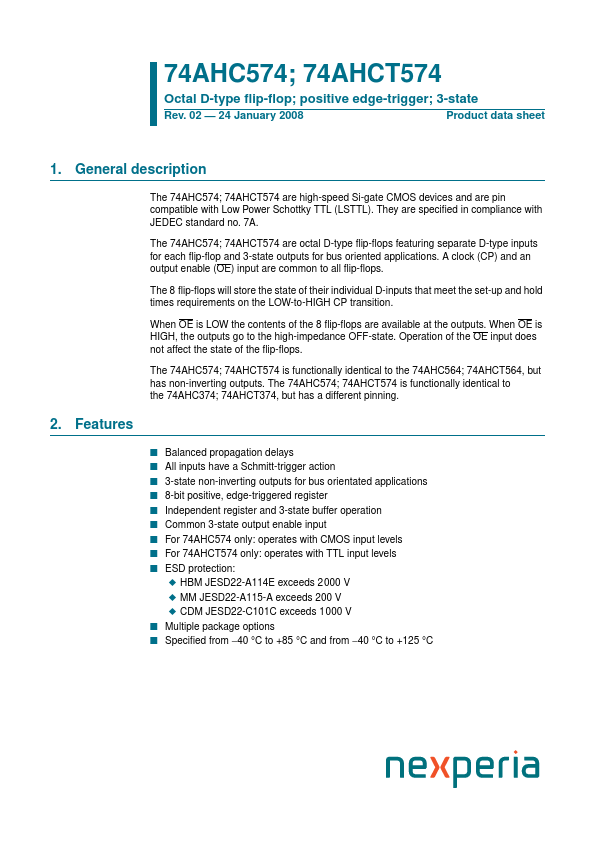

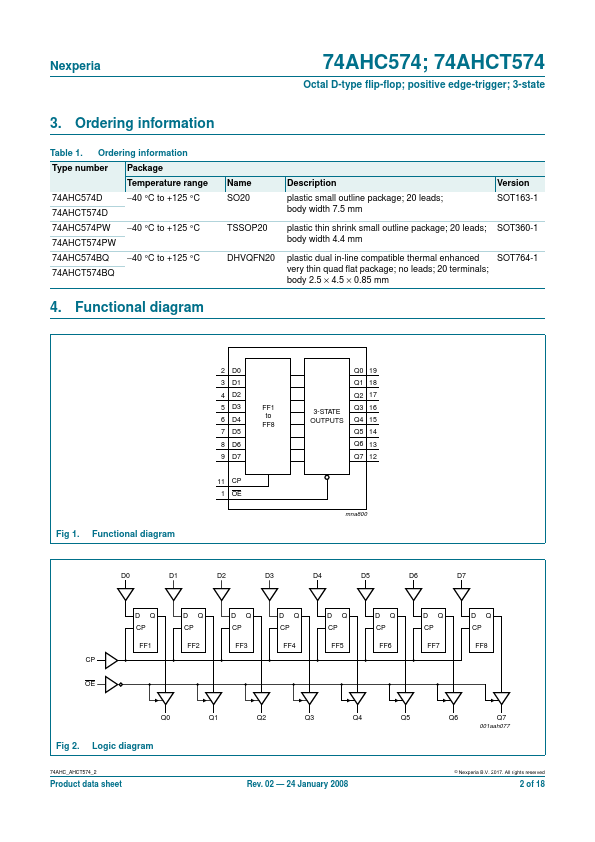

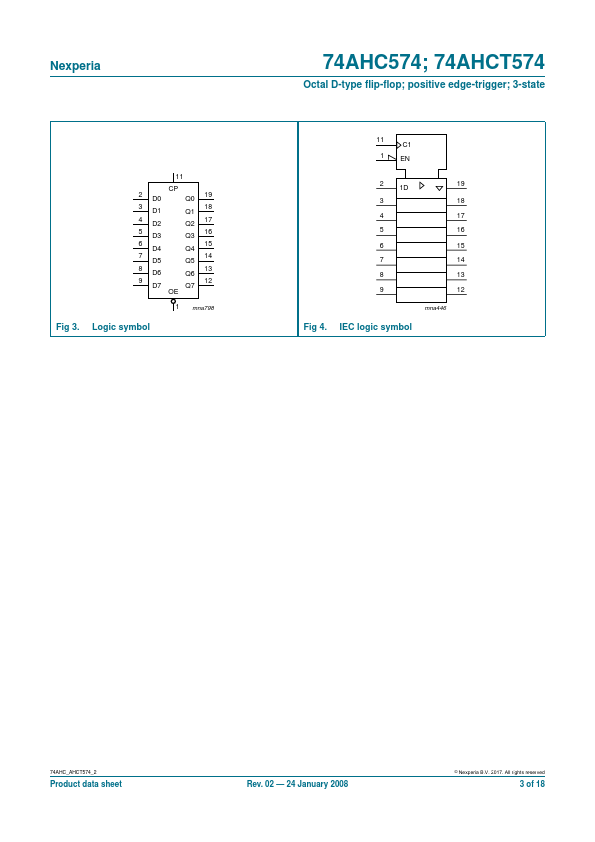

74AHCT574 are high-speed Si-gate CMOS devices and are pin patible with Low Power Schottky TTL (LSTTL). They are specified in pliance with JEDEC standard no. 74AHCT574 are octal D-type flip-flops featuring separate D-type inputs for each flip-flop and 3-state outputs for bus oriented applications.