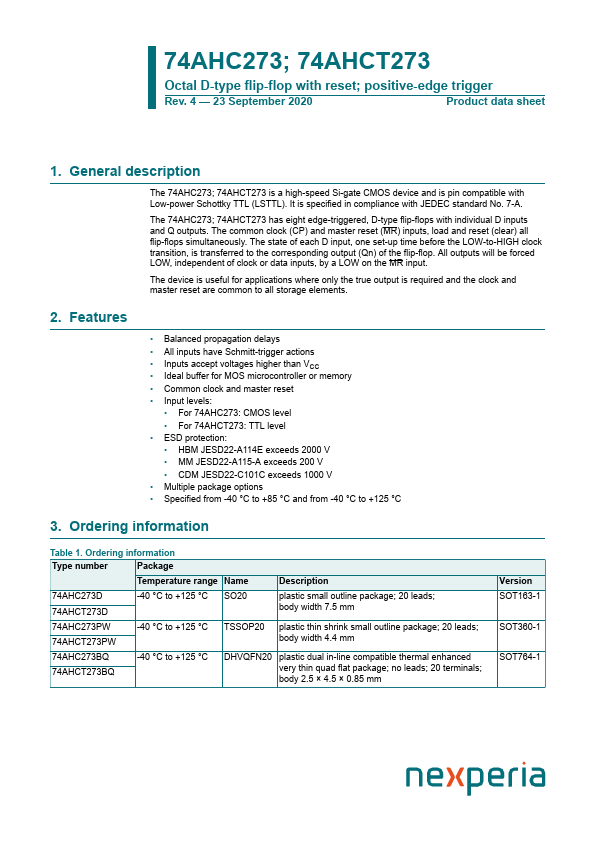

- Part: 74AHCT273PW

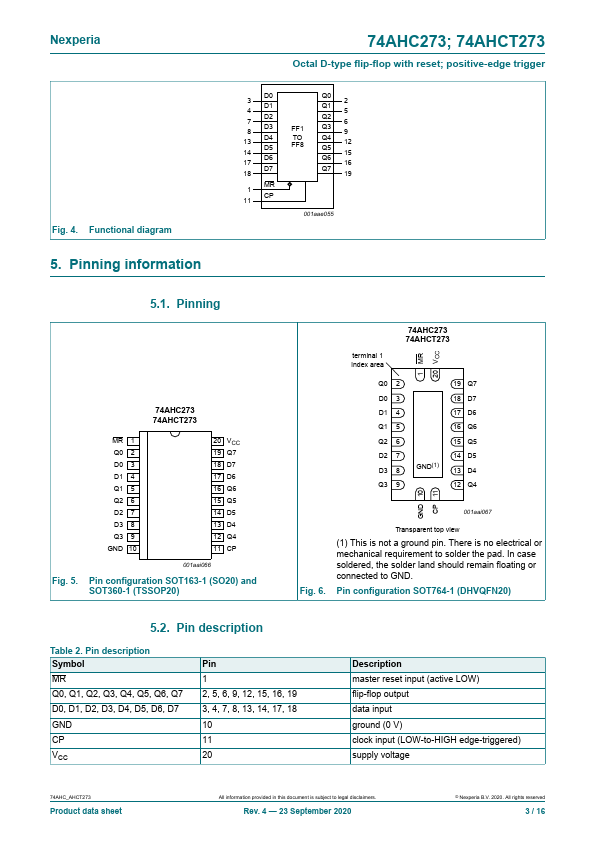

- Description: Octal D-type flip-flop

- Manufacturer: Nexperia

- Size: 265.73 KB

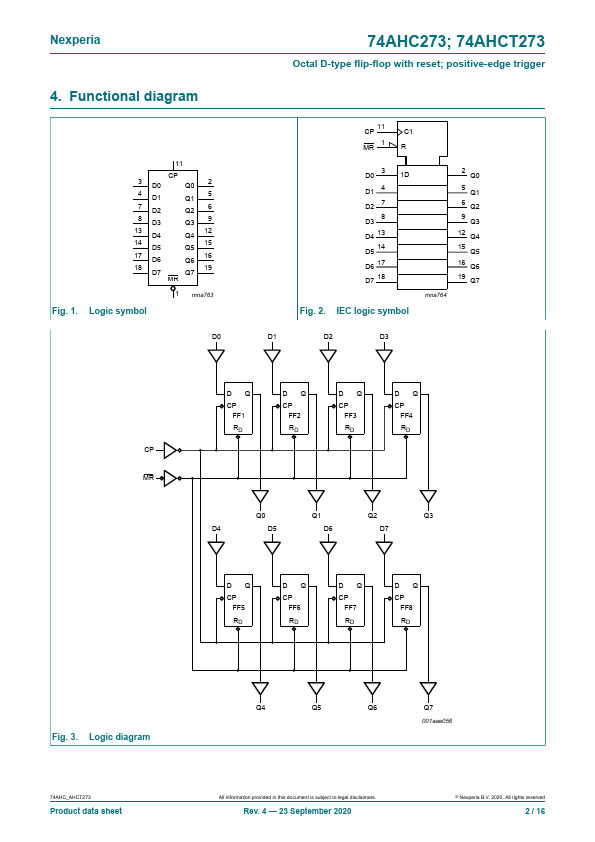

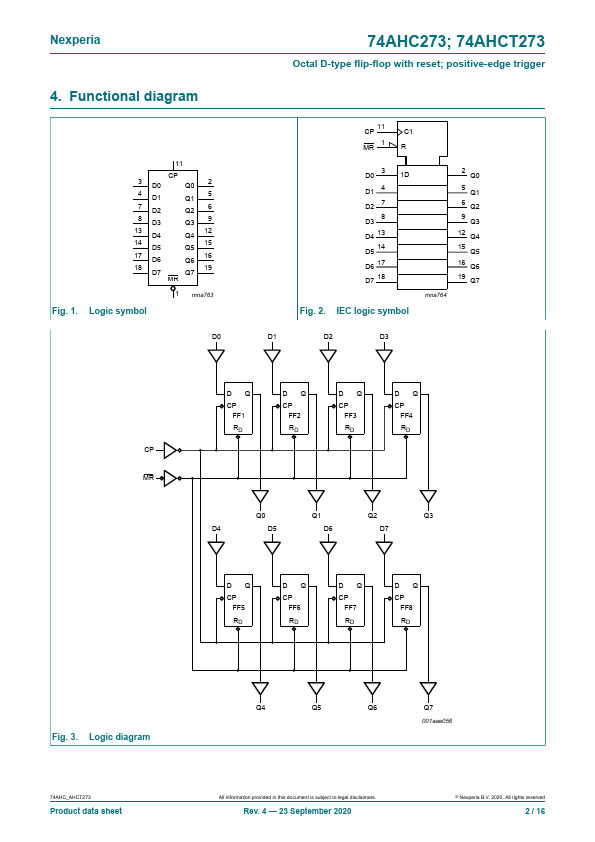

Page 2

Page 2

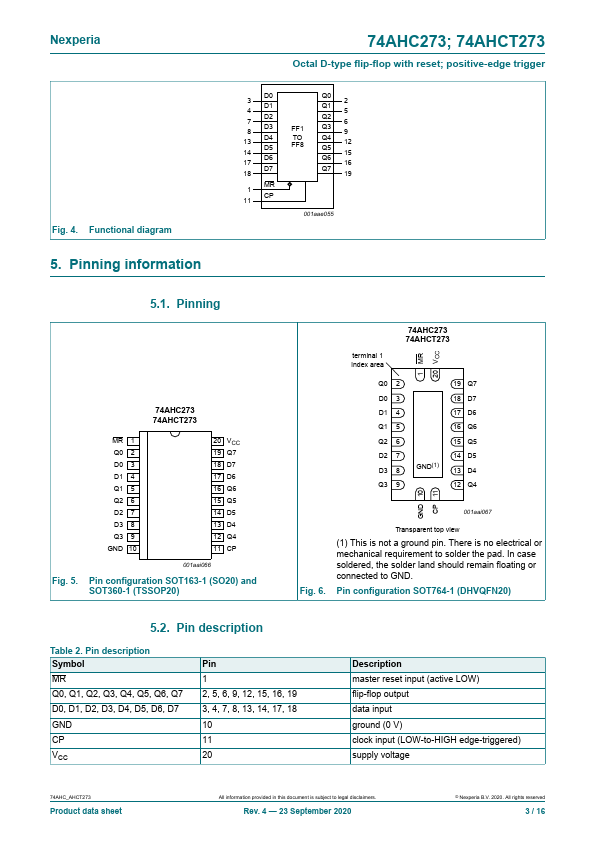

Page 3

Page 3

74AHCT273PW Key Features

- Balanced propagation delays

- All inputs have Schmitt-trigger actions

- Inputs accept voltages higher than VCC

- Ideal buffer for MOS microcontroller or memory

- mon clock and master reset

- Input levels

- For 74AHC273: CMOS level

- For 74AHCT273: TTL level

- ESD protection

- HBM JESD22-A114E exceeds 2000 V

Other 74AHCT273PW Datasheets

| Manufacturer |

Part Number |

Description |

NXP Semiconductors

NXP Semiconductors |

74AHCT273

|

Octal D-type flip-flop |