Datasheet Summary

74AHC2G125; 74AHCT2G125

Dual buffer/line driver; 3-state

Rev. 4

- 2 January 2019

Product data sheet

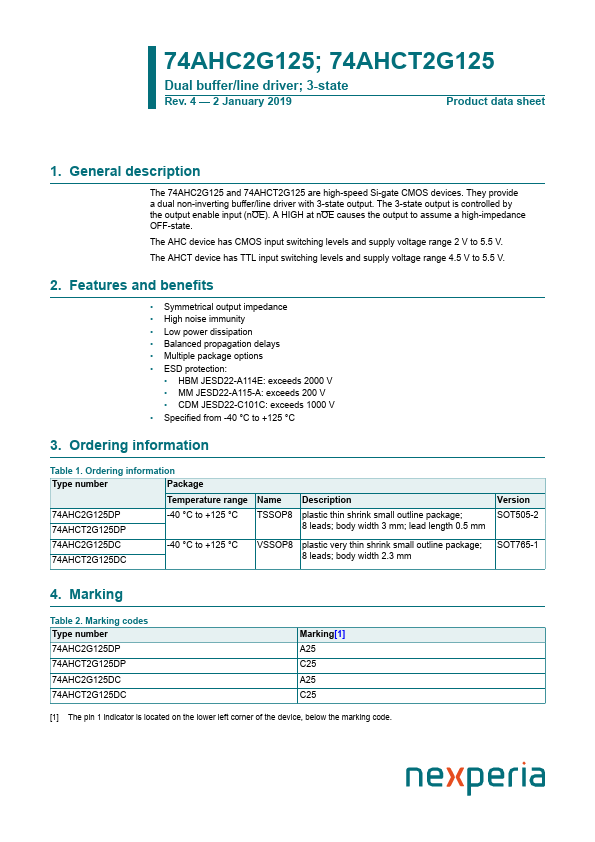

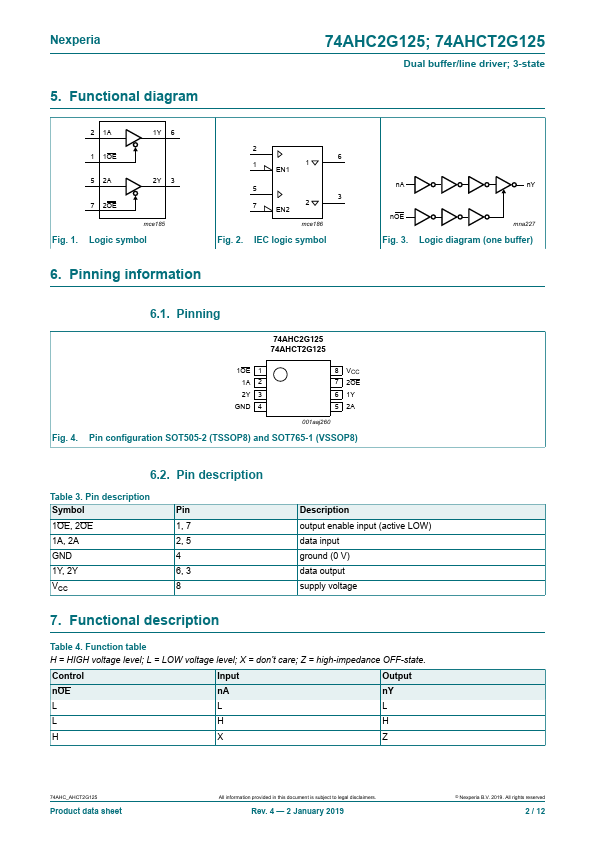

1. General description

The 74AHC2G125 and 74AHCT2G125 are high-speed Si-gate CMOS devices. They provide a dual non-inverting buffer/line driver with 3-state output. The 3-state output is controlled by the output enable input (nOE). A HIGH at nOE causes the output to assume a high-impedance OFF-state.

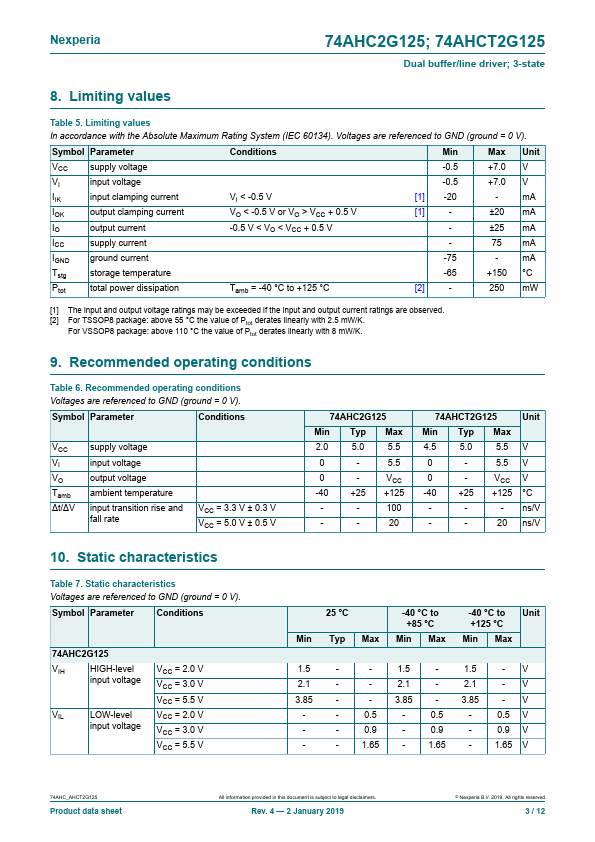

The AHC device has CMOS input switching levels and supply voltage range 2 V to 5.5 V.

The AHCT device has TTL input switching levels and supply voltage range 4.5 V to 5.5 V.

2. Features and benefits

- Symmetrical output impedance

- High noise immunity

- Low power dissipation

- Balanced...