74ALVCH16827DGG

74ALVCH16827DGG is 20-bit buffer/line driver manufactured by Nexperia.

- Part of the 74ALVCH16827 comparator family.

- Part of the 74ALVCH16827 comparator family.

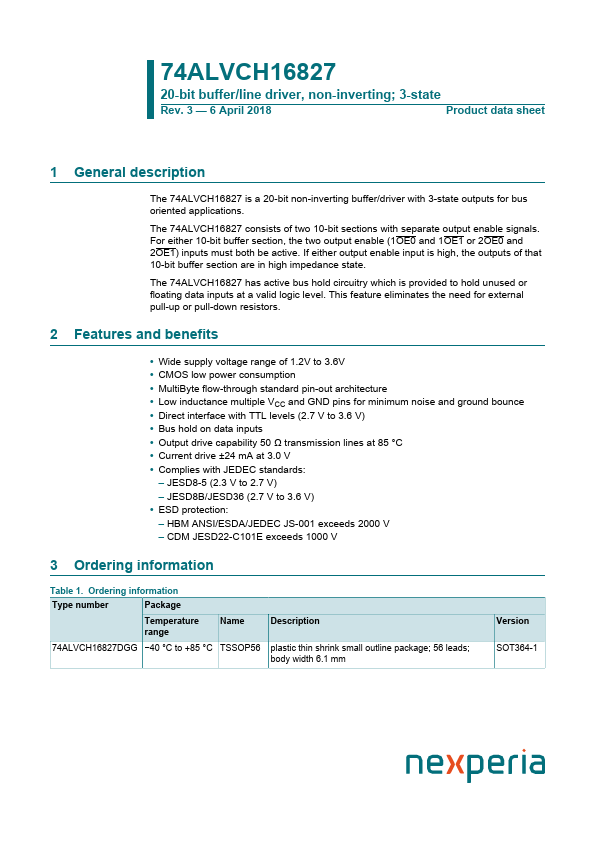

74ALVCH16827

20-bit buffer/line driver, non-inverting; 3-state

Rev. 3

- 6 April 2018

Product data sheet

1 General description

The 74ALVCH16827 is a 20-bit non-inverting buffer/driver with 3-state outputs for bus oriented applications.

The 74ALVCH16827 consists of two 10-bit sections with separate output enable signals. For either 10-bit buffer section, the two output enable (1OE0 and 1OE1 or 2OE0 and 2OE1) inputs must both be active. If either output enable input is high, the outputs of that 10-bit buffer section are in high impedance state.

The 74ALVCH16827 has active bus hold circuitry which is provided to hold unused or floating data inputs at a valid logic level. This feature...