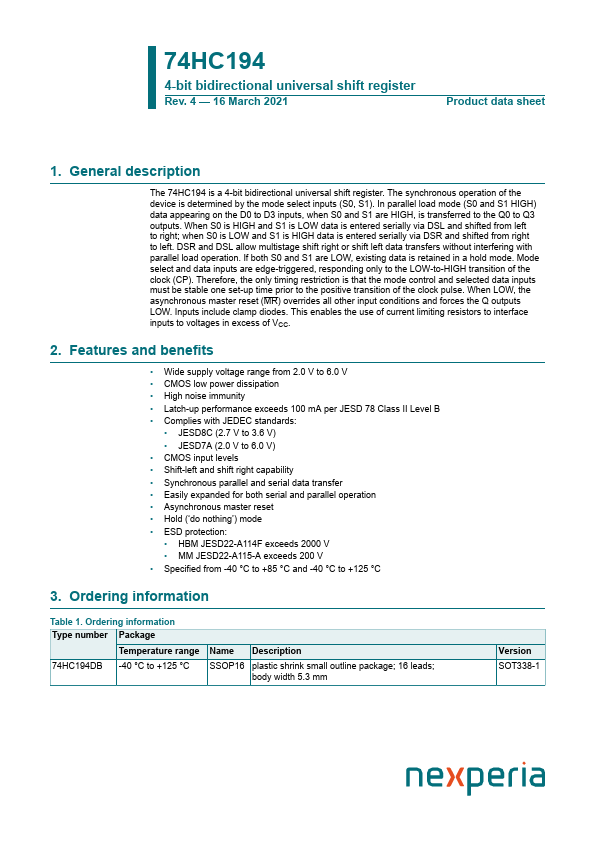

74HC194D Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 4.5 V

Description

The 74HC194 is a 4-bit bidirectional universal shift register. The synchronous operation of the device is determined by the mode select inputs (S0, S1).

Key Features

- Wide supply voltage range from 2.0 V to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- Complies with JEDEC standards