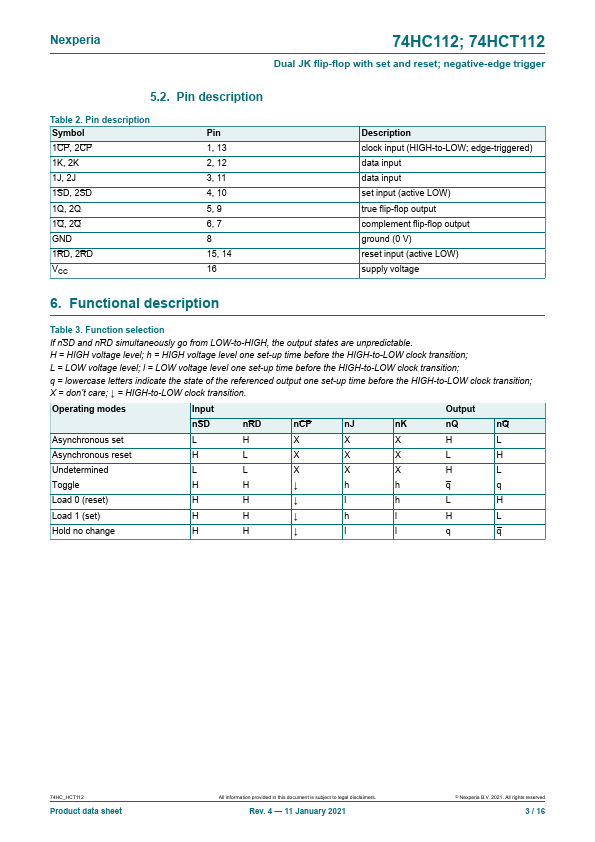

74HCT112 Description

74HCT112 is a dual negative-edge triggered JK flip-flop.

74HCT112 Key Features

- Input levels

- For 74HC112: CMOS level

- For 74HCT112: TTL level

- Asynchronous set and reset

- Specified in pliance with JEDEC standard no. 7A

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- 40 °C to +125 °C