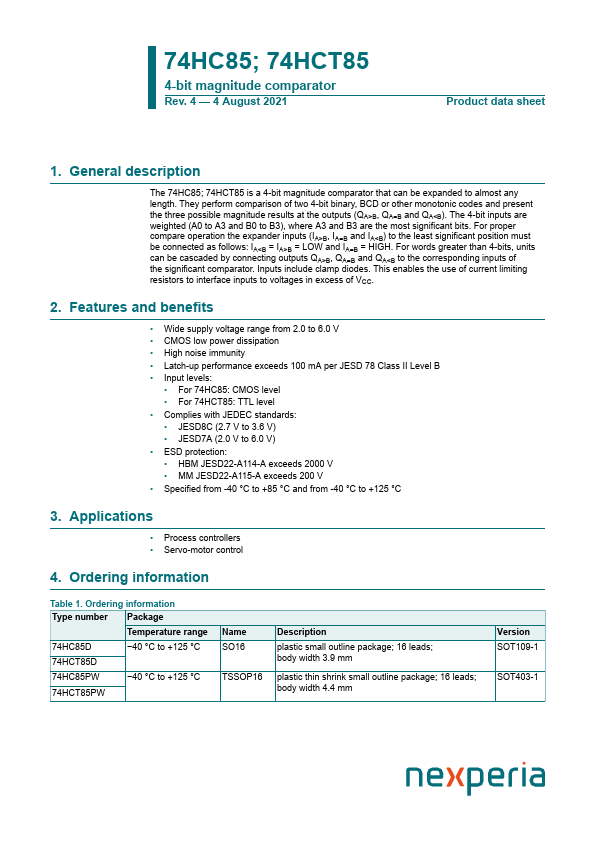

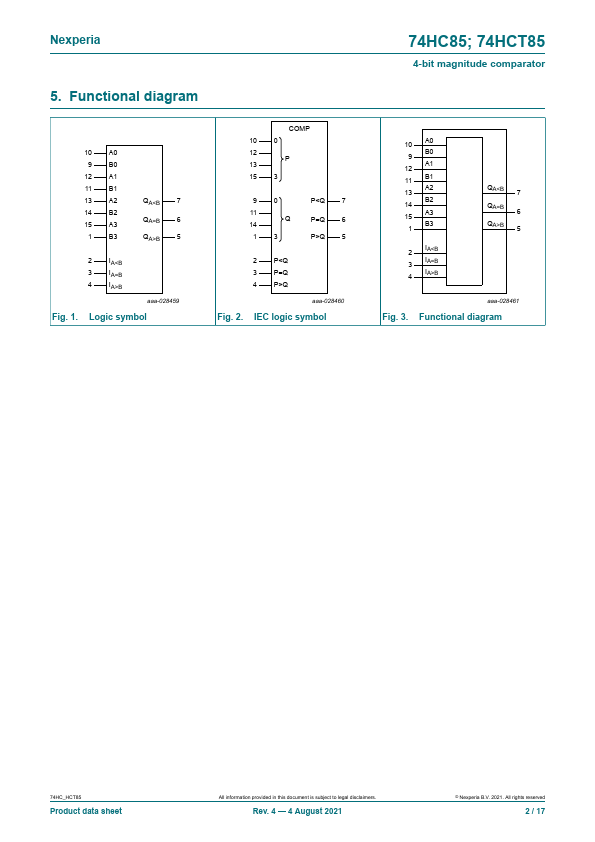

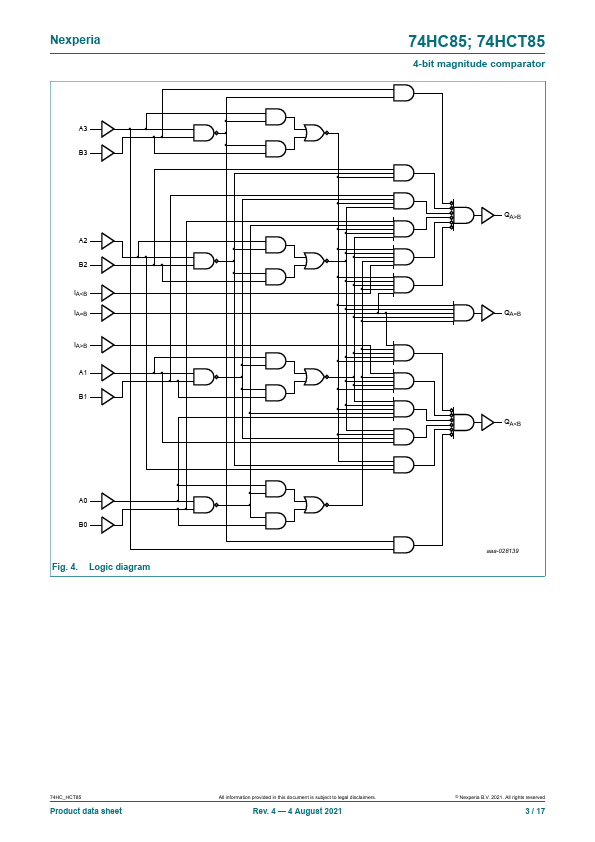

74HCT85 Description

74HCT85 is a 4-bit magnitude parator that can be expanded to almost any length. They perform parison of two 4-bit binary, BCD or other monotonic codes and present the three possible magnitude results at the outputs (QA>B, QA=B and QA<B). The 4-bit inputs are weighted (A0 to A3 and B0 to B3), where A3 and B3 are the most significant bits.

74HCT85 Key Features

- Wide supply voltage range from 2.0 to 6.0 V

- CMOS low power dissipation

- High noise immunity

- Latch-up performance exceeds 100 mA per JESD 78 Class II Level B

- Input levels

- For 74HC85: CMOS level

- For 74HCT85: TTL level

- plies with JEDEC standards

- JESD8C (2.7 V to 3.6 V)

- JESD7A (2.0 V to 6.0 V)