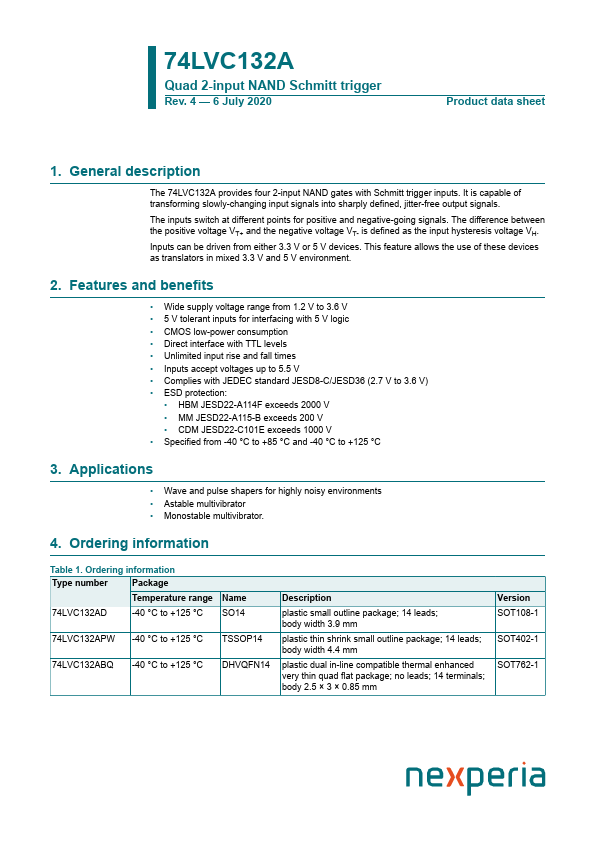

74LVC132APW Description

The 74LVC132A provides four 2-input NAND gates with Schmitt trigger inputs. It is capable of transforming slowly-changing input signals into sharply defined, jitter-free output signals. The inputs switch at different points for positive and negative-going signals.

74LVC132APW Key Features

- Wide supply voltage range from 1.2 V to 3.6 V

- 5 V tolerant inputs for interfacing with 5 V logic

- CMOS low-power consumption

- Direct interface with TTL levels

- Unlimited input rise and fall times

- Inputs accept voltages up to 5.5 V

- plies with JEDEC standard JESD8-C/JESD36 (2.7 V to 3.6 V)

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

- MM JESD22-A115-B exceeds 200 V

74LVC132APW Applications

- Wave and pulse shapers for highly noisy environments