HEF4020B-Q100 Description

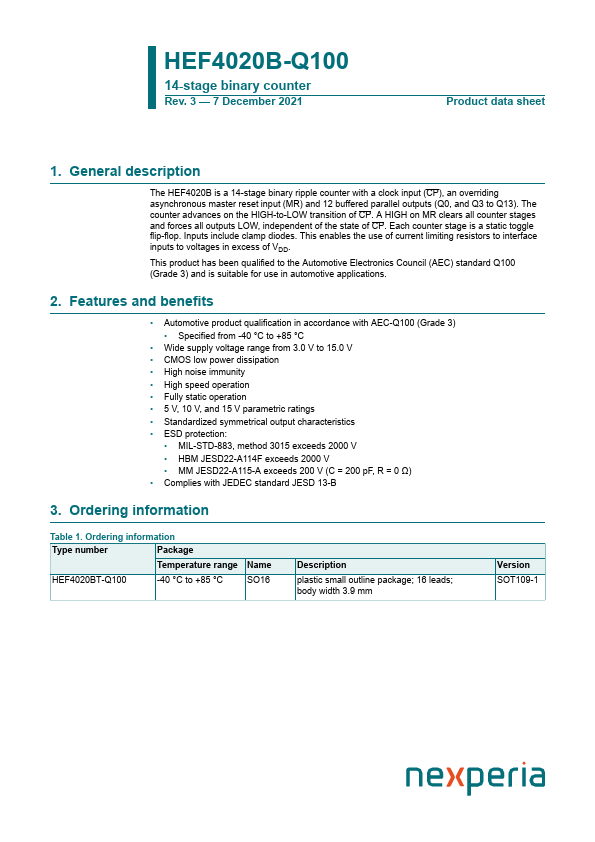

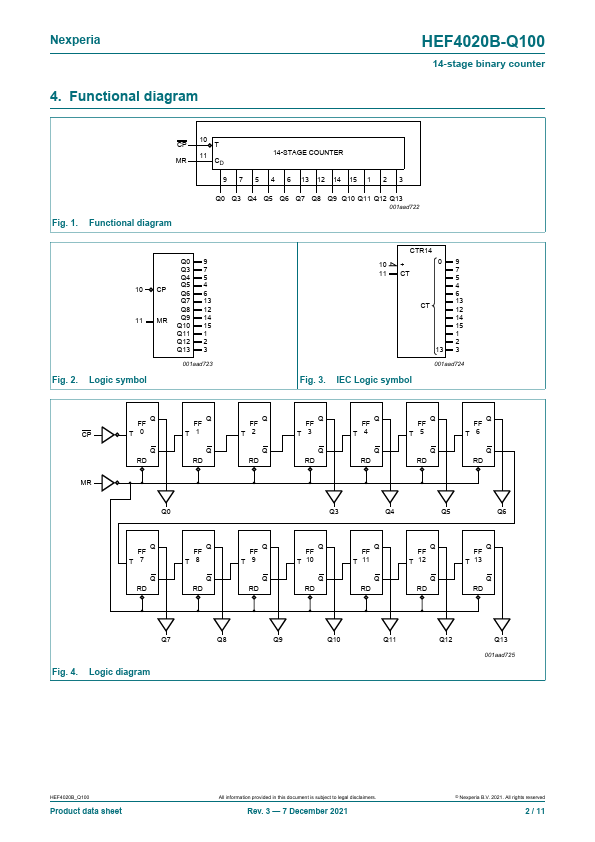

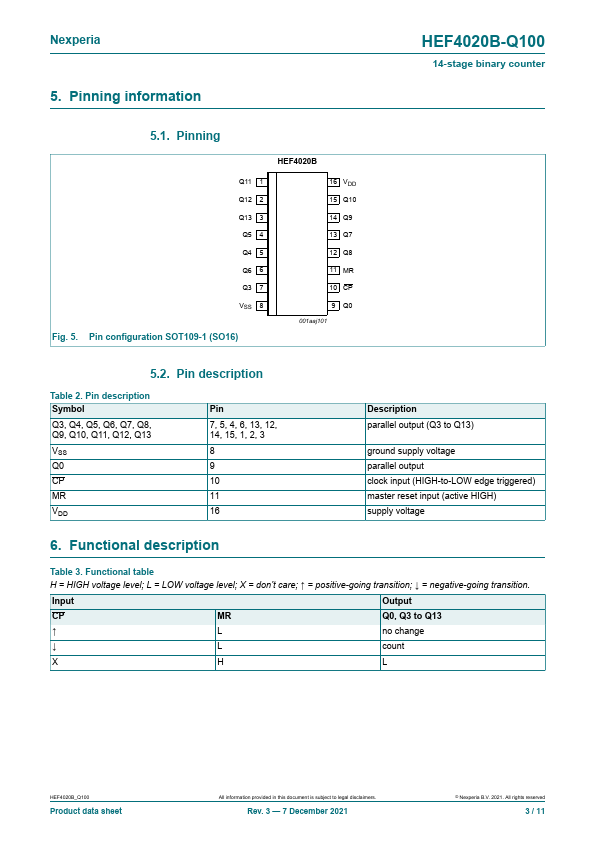

The HEF4020B is a 14-stage binary ripple counter with a clock input (CP), an overriding asynchronous master reset input (MR) and 12 buffered parallel outputs (Q0, and Q3 to Q13). The counter advances on the HIGH-to-LOW transition of CP. A HIGH on MR clears all counter stages and forces all outputs LOW, independent of the state of CP.

HEF4020B-Q100 Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade 3)

- Specified from -40 °C to +85 °C

- Wide supply voltage range from 3.0 V to 15.0 V

- CMOS low power dissipation

- High noise immunity

- High speed operation

- Fully static operation

- 5 V, 10 V, and 15 V parametric ratings

- Standardized symmetrical output characteristics

- ESD protection

HEF4020B-Q100 Applications

- Automotive product qualification in accordance with AEC-Q100 (Grade 3)

- Specified from -40 °C to +85 °C

- Wide supply voltage range from 3.0 V to 15.0 V