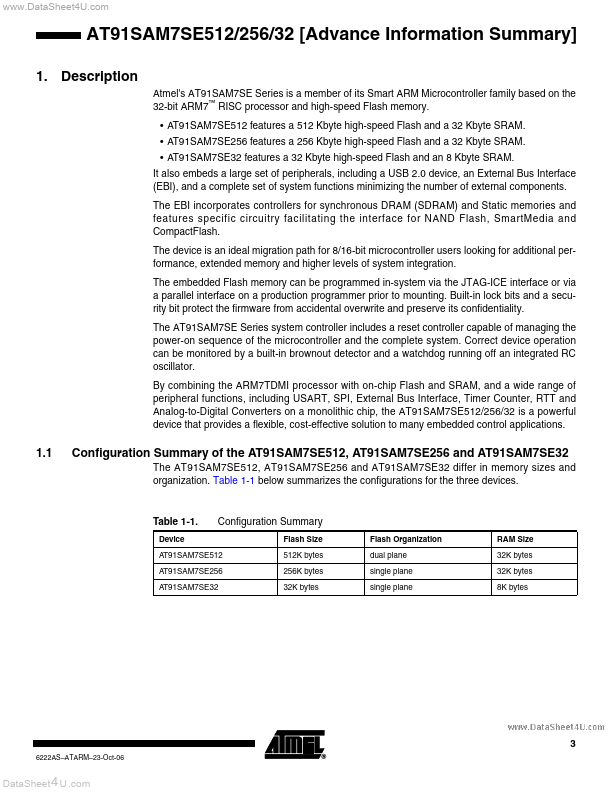

Description

AT91SAM7SE512 AT91SAM7SE256 AT91SAM7SE32

Advance Information Summary

NOTE: This is a summary document.

ATARM

23-Oct-06

DataSheet 4 U .com

www.DataSheet4U.com

Counter May Be Stopped While the Processor is in Debug State or in Idle Mode

Real-time Timer (RTT)

32-

Features

- Incorporates the ARM7TDMI® ARM® Thumb® Processor.

- High-performance 32-bit RISC Architecture.

- High-density 16-bit Instruction Set.

- Leader in MIPS/Watt.

- EmbeddedICE™ In-circuit Emulation, Debug Communication Channel Support Internal High-speed Flash.

- 512 Kbytes, Organized in Two Contiguous Banks of 1024 Pages of 256 Bytes Dual Plane (AT91SAM7SE512).

- 256 Kbytes (AT91SAM7SE256) Organized in One Bank of 1024 Pages of 256 Bytes Single Pla.