Description

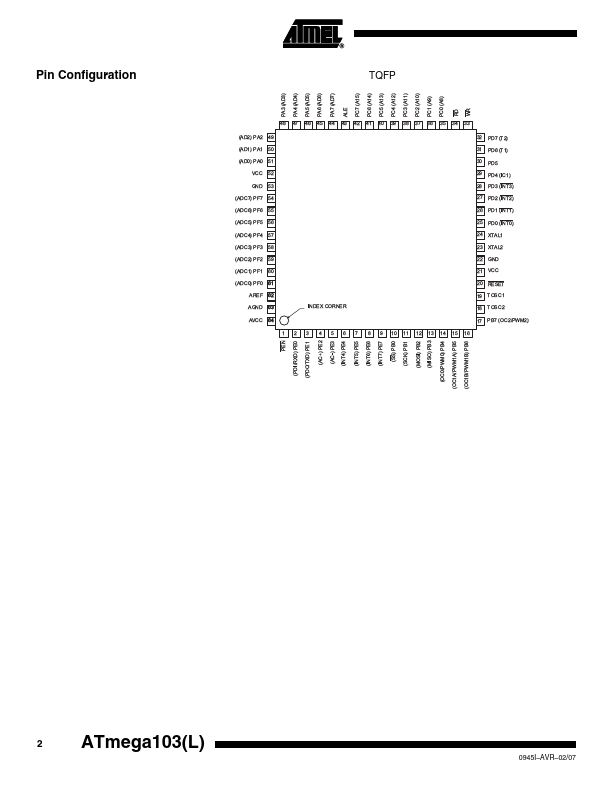

ATmega103(L)

The ATmega103(L) is a low-power, CMOS, 8-bit microcontroller based on the AVR RISC architecture.By executing powerful instructions in a single clock cycle, the ATmega103(L) achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.The AVR core is based on an enhanced RISC architecture that combines a rich instruction set with 32 general purpose working registers.All the 32 registers are directly connected

Features

- Utilizes the AVR® RISC Architecture.

- AVR.

- High-performance and Low-power RISC Architecture.

- 121 Powerful Instructions.

- Most Single Clock Cycle Execution.

- 32 x 8 General Purpose Working Registers + Peripheral Control Registers.

- Up to 6 MIPS Throughput at 6 MHz.

- Data and Nonvolatile Program Memory.

- 128K Bytes of In-System Programmable Flash

Endurance: 1,000 Write/Erase Cycles.

- 4K Bytes Internal SRAM.