Description

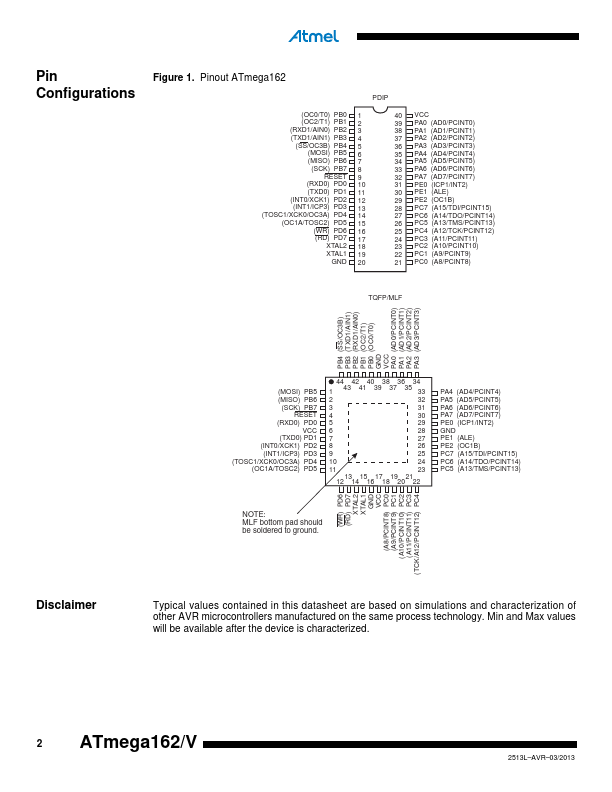

VCC GND Port A (PA7..PA0)

Port B (PB7..PB0)

Port C (PC7..PC0)

The timed sequence for changing the Watchdog Time-out period is disabled.

The double buffering of the USART Receive Registers is disabled.

Compatibility” on page 168 for details.

Pin change interrupts are not supported (Control Registers are located in Extended I/O).

Features

- High-performance, Low-power AVR® 8-bit Microcontroller.

- Advanced RISC Architecture.

- 131 Powerful Instructions.

- Most Single-clock Cycle Execution.

- 32 x 8 General Purpose Working Registers.

- Fully Static Operation.

- Up to 16 MIPS Throughput at 16 MHz.

- On-chip 2-cycle Multiplier.

- High Endurance Non-volatile Memory segments.

- 16K Bytes of In-System Self-programmable Flash program memory.

- 512 Bytes EEPROM.