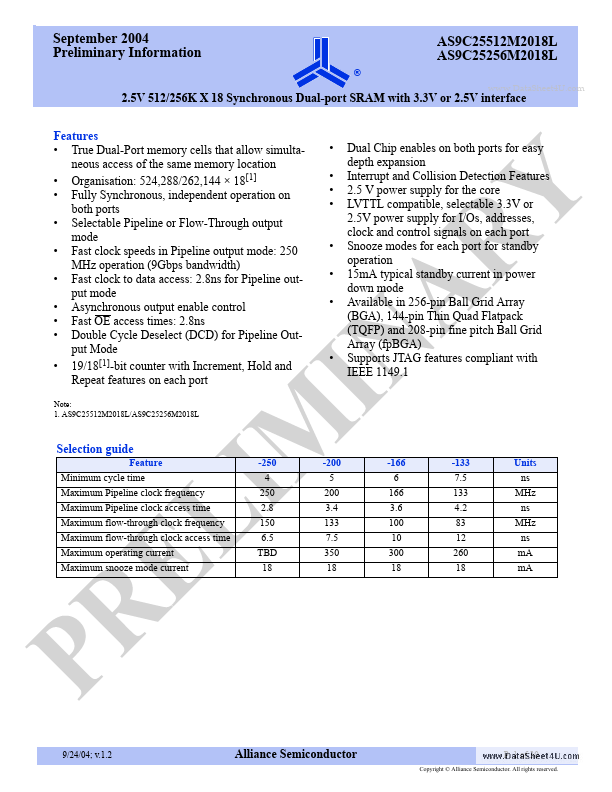

AS9C25512M2018L

Features

- True Dual-Port memory cells that allow simultaneous access of the same memory location

- Organisation: 524,288/262,144 × 18[1]

- Fully Synchronous, independent operation on both ports

- Selectable Pipeline or Flow-Through output mode

- Fast clock speeds in Pipeline output mode: 250 MHz operation (9Gbps bandwidth)

- Fast clock to data access: 2.8ns for Pipeline output mode

- Asynchronous output enable control

- Fast OE access times: 2.8ns

- Double Cycle Deselect (DCD) for Pipeline Output Mode

- 19/18[1]-bit counter with Increment, Hold and Repeat features on each port

Note: 1. AS9C25512M2018L/AS9C25256M2018L

- -

- -

- -

- -

Dual Chip enables on both ports for easy depth expansion Interrupt and Collision Detection Features

2.5 V power supply for the core LVTTL patible, selectable 3.3V or 2.5V power supply for I/Os, addresses, clock and control signals on each port Snooze modes for each port for standby operation 15m A typical standby current in power down mode Available in...