EDS2504APTA

Description

The EDS2504AP is a 256M bits SDRAM organized as 16,777,216 words × 4 bits × 4 banks. The EDS2508 AP is a 256M bits SDRAM organized as 8,388,608 words × 8 bits × 4 banks. The EDS2516 AP is a 256M bits SDRAM organized as 4194304 words × 16 bits × 4 banks. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54pin plastic TSOP (II).

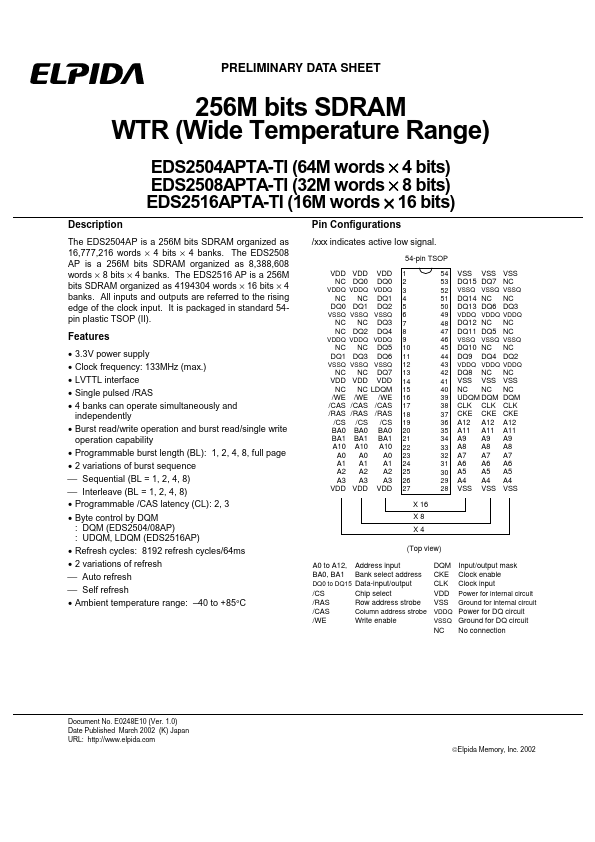

Pin Configurations

/xxx indicates active low signal.

54-pin TSOP VDD VDD NC DQ0 NC NC DQ0 DQ1 NC NC NC DQ2 NC NC DQ1 DQ3 NC VDD NC /WE /CAS /RAS /CS BA0 BA1 A10 A0 A1 A2 A3 VDD VDD DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

VSS VSS VSS DQ15 DQ7 NC

VSSQ VSSQ VSSQ

VDDQ VDDQ VDDQ

DQ14 NC NC DQ13 DQ6 DQ3

VDDQ VDDQ VDDQ

VSSQ VSSQ VSSQ

Features

- -

- -

- 3.3V power supply Clock frequency: 133MHz (max.) LVTTL interface Single pulsed /RAS 4 banks can operate...