IC41C16105

DESCRIPTION

The 1+51 IC41C16105 and IC41LV16105 are 1,048,576 x

16-bit high-performance CMOS Dynamic Random Access Memories. .ast Page Mode allows 1,024 random accesses within a single row with access cycle time as short as 20 ns per 16-bit word. The Byte Write control, of upper and lower byte, makes the IC41C16105 ideal for use in 16-, 32-bit wide data bus systems. These features make the IC41C16105 and IC41LV16105 ideally suited for high-bandwidth graphics, digital signal processing, high-performance puting systems, and peripheral applications. The IC41C16105 and IC41LV16105 are packaged in a 42-pin 400mil SOJ and 400mil 44- (50-) pin TSOP-2.

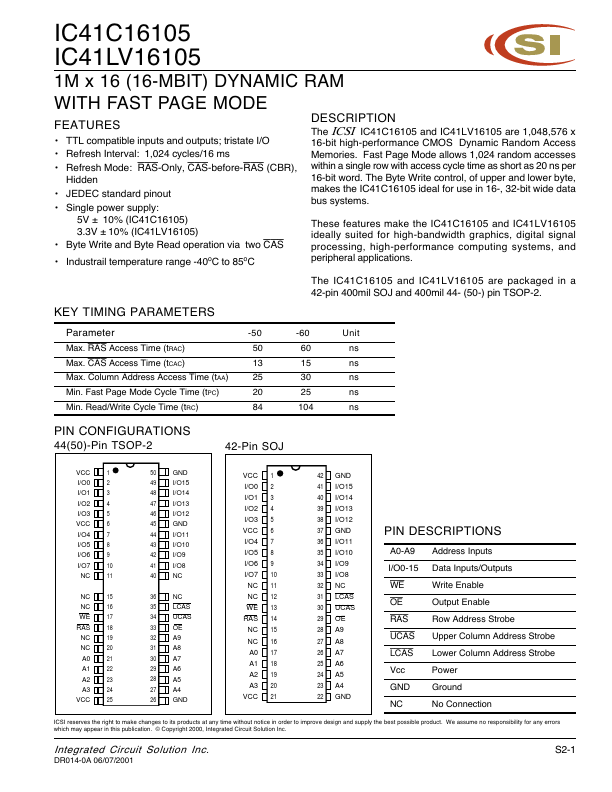

KEY TIMING PARAMETERS

Parameter

Max. RAS Access Time (t RAC) Max. CAS Access Time (t CAC) Max. Column Address Access Time (t AA) Min. .ast Page Mode Cycle Time (t PC) Min. Read/Write Cycle Time (t RC) -50 50 13 25 20 84 -60 60 15 30 25 104 Unit ns ns ns ns ns

PIN CON.IGURATIONS

44(50)-Pin TSOP-2

VCC I/O0 I/O1 I/O2 I/O3 VCC I/O4 I/O5 I/O6 I/O7 NC...