IN74HC112A

TECHNICAL DATA

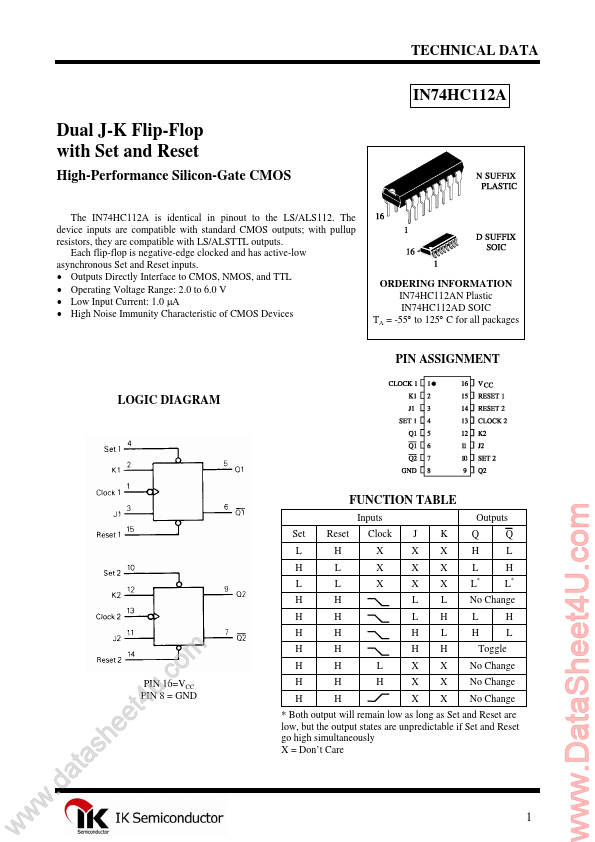

Dual J-K Flip-Flop with Set and Reset

High-Performance Silicon-Gate CMOS

The IN74HC112A is identical in pinout to the LS/ALS112. The device inputs are patible with standard CMOS outputs; with pullup resistors, they are patible with LS/ALSTTL outputs. Each flip-flop is negative-edge clocked and has active-low asynchronous Set and Reset inputs.

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1.0 µA

- High Noise Immunity Characteristic of CMOS Devices

ORDERING INFORMATION IN74HC112AN Plastic IN74HC112AD SOIC TA = -55° to 125° C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

Inputs Set L H L H H H Reset H L L H H H H H H H L H Clock X X X J X X X L L H H X X X K X X X L H L H X X X

Outputs Q H L L

- Q L H L- H L

No Change L H w w w

.d h s a t a ee

. u t4

PIN 16=VCC PIN 8 = GND m o c

Toggle No Change No Change No Change

- Both output will remain low as long as Set and...