IN74HC573A

TECHNICAL DATA

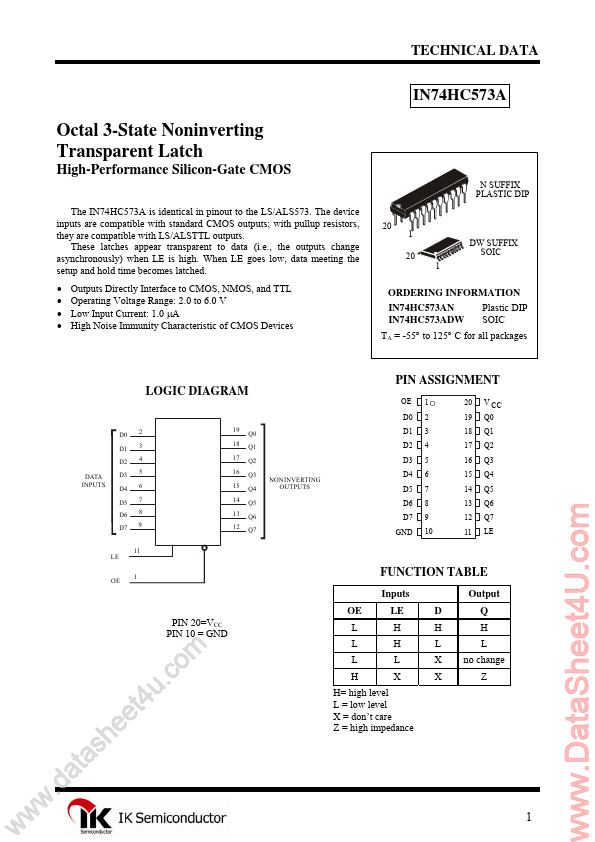

Octal 3-State Noninverting Transparent Latch

High-Performance Silicon-Gate CMOS

N SUFFIX PLASTIC DIP

The IN74HC573A is identical in pinout to the LS/ALS573. The device inputs are patible with standard CMOS outputs; with pullup resistors, they are patible with LS/ALSTTL outputs. These latches appear transparent to data (i.e., the outputs change asynchronously) when LE is high. When LE goes low, data meeting the setup and hold time bees latched.

- -

- - Outputs Directly Interface to CMOS, NMOS, and TTL Operating Voltage Range: 2.0 to 6.0 V Low Input Current: 1.0 µA High Noise Immunity Characteristic of CMOS Devices

1 20 1

DW SUFFIX SOIC

ORDERING INFORMATION IN74HC573AN IN74HC573ADW Plastic DIP SOIC

TA = -55° to 125° C for all packages

PIN ASSIGNMENT LOGIC DIAGRAM

19 18 17 16 15 14 13 12

OE D0

1 2 3 4 5 6 7 8 9 10

20 19 18 17 16 15 14 13 12 11

V CC Q0 Q1 Q2 Q3 Q4 Q5

D0 D1 D2 DATA INPUTS D3 D4 D5 D6 D7

2 3 4 5 6 7 8 9

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7...