IS61LPD102418A Overview

Key Specifications

Pins: 165

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Min Voltage (typical range): 3.135 V

Description

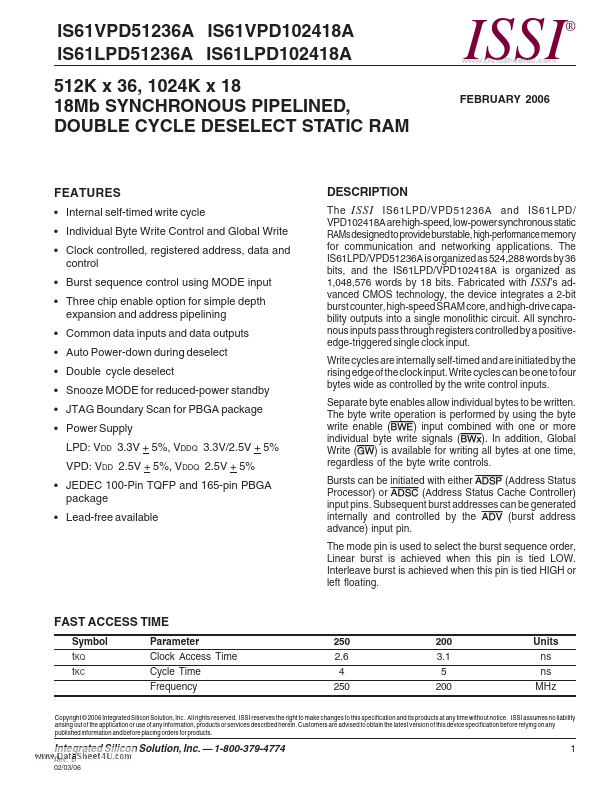

The ISSI IS61LPD/VPD51236A and IS61LPD/ VPD102418A are high-speed, low-power synchronous static RAMs designed to provide burstable, high-performance memory for communication and networking applications. The IS61LPD/VPD51236A is organized as 524,288 words by 36 bits, and the IS61LPD/VPD102418A is organized as 1,048,576 words by 18 bits.

Key Features

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and control

- Burst sequence control using MODE input

- Three chip enable option for simple depth expansion and address pipelining