Description

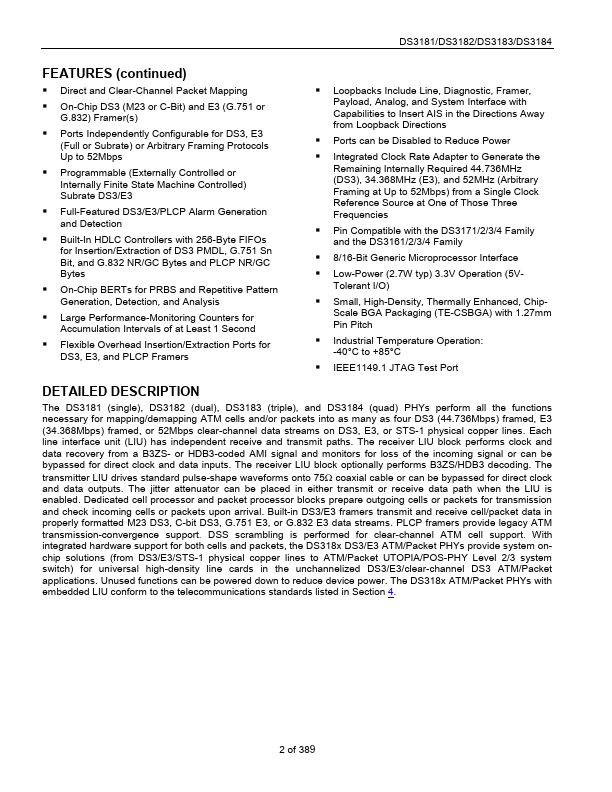

The DS3181, DS3182, DS3183, and DS3184 (DS318x) integrate ATM cell/HDLC packet processor(s) with a DS3/E3 framer(s) and LIU(s) to map/demap ATM cells or packets into as many as four DS3/E3 physical copper lines with DS3-framed, E3-framed, or clear-channel data streams on per-port basis.

Features

- Single (DS3181), Dual (DS3182), Triple (DS3183), or Quad (DS3184) with Integrated LIU ATM/Packet PHYs for DS3, E3, and ClearChannel 52Mbps (CC52) Pin Compatible for Ease of Port Density Migration in the Same PC Board Platform Each Port Independently Configurable Perform Receive Clock/Data Recovery and Transmit Waveshaping Jitter Attenuator can be Placed Either in the Receive or Transmit Paths Interfaces to 75W Coaxial Cable at Lengths Up to 380 Meters or 1246 Feet (DS3) or 440 Meters or 14.