SY100E107

FEATURES s 600ps max. propagation delay s Extended 100E VEE range of

- 4.2V to

- 5.5V s True and plementary outputs s OR/NOR function outputs s Fully patible with Industry standard 10KH,

100K I/O levels s Internal 75KΩ input pulldown resistors s Fully patible with Motorola MC10E/100E107 s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E107 offer five 2-input XOR/XNOR gates and are designed for use in new, high- performance ECL systems.

The E107 also features a function output, F, which is the OR of all five XOR gate outputs, while F is the NOR. Both true and plementary outputs are provided.

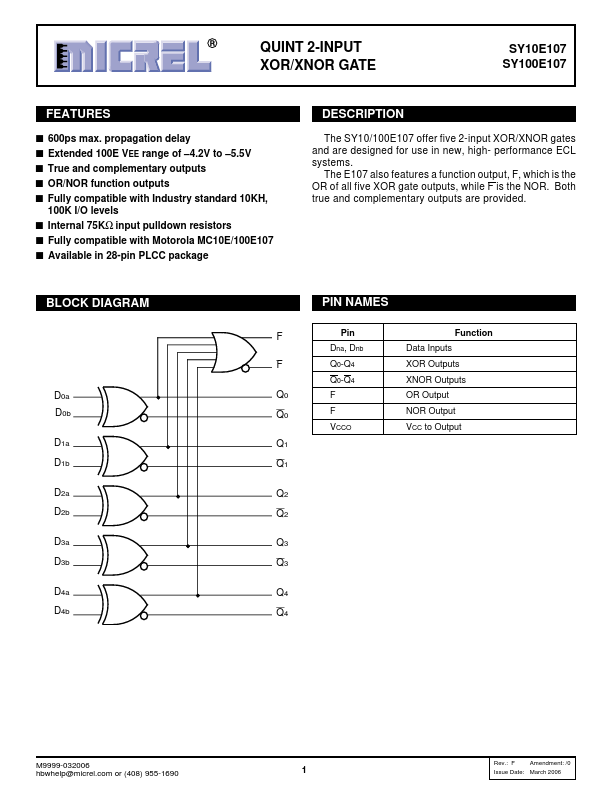

BLOCK DIAGRAM

D0a D0b D1a D1b D2a D2b D3a D3b D4a D4b

PIN NAMES

F Pin

Function

Dna, Dnb

Data Inputs

F Q0-Q4 Q0-Q4

Q0 F

XOR Outputs XNOR Outputs OR Output

Q0 F VCCO

NOR Output VCC to Output

Q1

Q1

Q2 Q2

Q3 Q3

Q4 Q4

M9999-032006 hbwhelp@micrel. or (408) 955-1690

Rev.: F Amendment: /0 Issue Date: March 2006

Micrel, Inc.

SY10E107 SY100E107

PACKAGE/ORDERING INFORMATION

Ord...