SY100E171

FEATURES s 725ps max. D to output s Extended 100E VEE range of

- 4.2V to

- 5.5V s Differential outputs s Split select architecture s Fully patible with industry standard 10KH,

100K ECL levels s Internal 75KΩ input pulldown resistors s Fully patible with Motorola MC10E/100E171 s Available in 28-pin PLCC package

DESCRIPTION

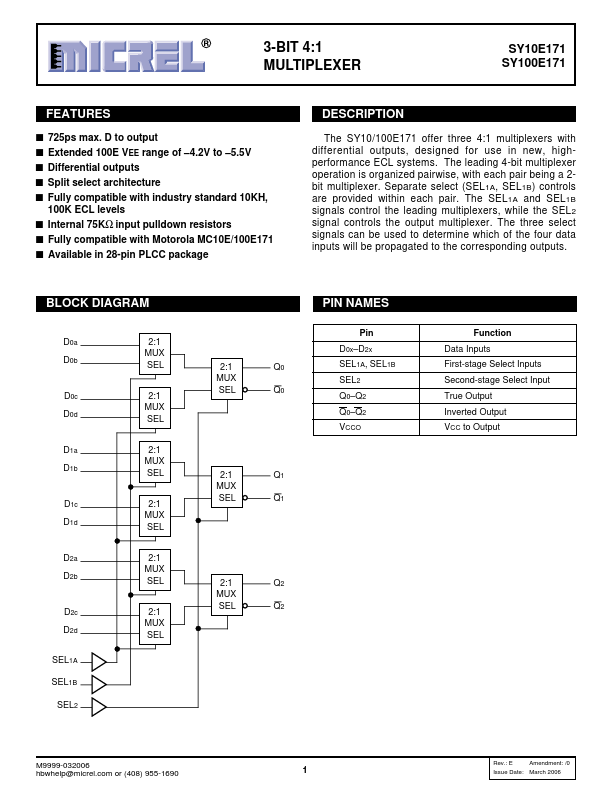

The SY10/100E171 offer three 4:1 multiplexers with differential outputs, designed for use in new, highperformance ECL systems. The leading 4-bit multiplexer operation is organized pairwise, with each pair being a 2bit multiplexer. Separate select (SEL1A, SEL1B) controls are provided within each pair. The SEL1A and SEL1B signals control the leading multiplexers, while the SEL2 signal controls the output multiplexer. The three select signals can be used to determine which of the four data inputs will be propagated to the corresponding outputs.

BLOCK DIAGRAM

D0a D0b

D0c D0d

D1a D1b

D1c D1d

D2a D2b

D2c D2d

SEL1A SEL1B

SEL2

2:1 MUX SEL

2:1 MUX SEL

2:1 MUX SEL

2:1 MUX...