SY100E452

FEATURES s Differential D, CLK and Q s Extended 100E VEE range of

- 4.2V to

- 5.5V s VBB output for single-ended use s 1100MHz min. toggle frequency s Asynchronous Master Reset s Fully patible with Motorola MC10E/100E452 s Available in 28-pin PLCC package

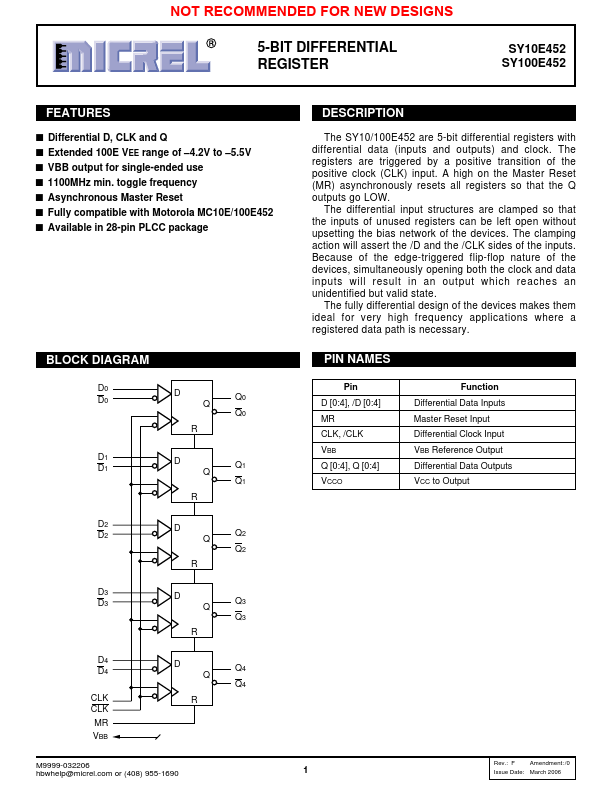

BLOCK DIAGRAM

D0 D0

D1 D1

D2 D2

D3 D3

D4 D4 CLK CLK MR VBB

M9999-032206 hbwhelp@micrel. or (408) 955-1690

Q0 Q0

Q1 Q1

Q2 Q2

Q3 Q3

Q4 Q4

DESCRIPTION

The SY10/100E452 are 5-bit differential registers with differential data (inputs and outputs) and clock. The registers are triggered by a positive transition of the positive clock (CLK) input. A high on the Master Reset (MR) asynchronously resets all registers so that the Q outputs go LOW.

The differential input structures are clamped so that the inputs of unused registers can be left open without upsetting the bias network of the devices. The clamping action will assert the /D and the /CLK sides of the inputs. Because of the edge-triggered flip-flop...