SY100EL56V

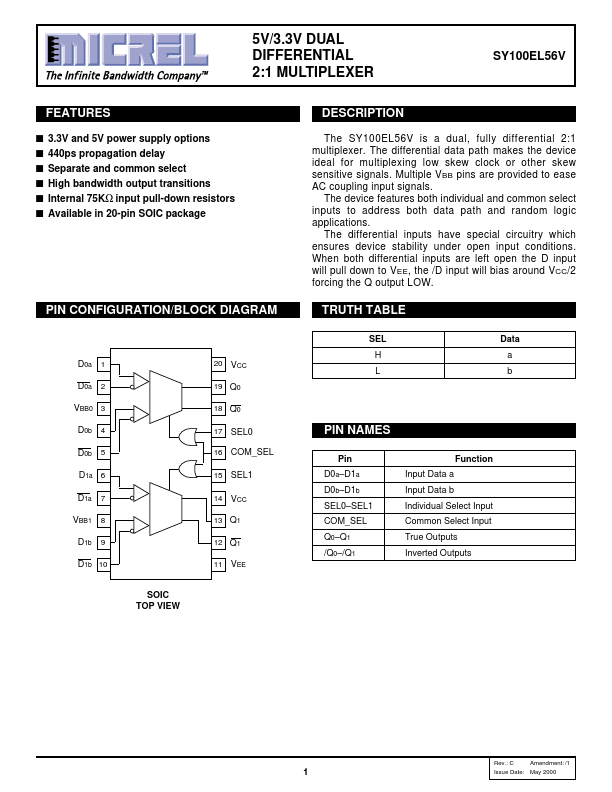

FEATURES s s s s s s 3.3V and 5V power supply options 440ps propagation delay Separate and mon select High bandwidth output transitions Internal 75KΩ input pull-down resistors Available in 20-pin SOIC package

DESCRIPTION

The SY100EL56V is a dual, fully differential 2:1 multiplexer. The differential data path makes the device ideal for multiplexing low skew clock or other skew sensitive signals. Multiple VBB pins are provided to ease AC coupling input signals. The device features both individual and mon select inputs to address both data path and random logic applications. The differential inputs have special circuitry which ensures device stability under open input conditions. When both differential inputs are left open the D input will pull down to VEE, the /D input will bias around VCC/2 forcing the Q output LOW.

PIN CONFIGURATION/BLOCK DIAGRAM

TRUTH TABLE

SEL H Data a b

D0a 1 D0a 2 VBB0 3 D0b 4 D0b 5 D1a 6 D1a

19 Q0 18 Q0 17 16 15 14

SEL0 _SEL SEL1...