SY10E212

FEATURES s Scannable version E112 driver s Extended 100E VEE range of

- 4.2V to

- 5.5V s 1025ps max. CLK to Output s Dual differential outputs s Master Reset s Internal 75KΩ input pull-down resistors s Fully patible with industry standard 10KH,

100K ECL levels s Fully patible with Motorola MC10E/100E212 s Available in 28-pin PLCC package

DESCRIPTION

The SY10/100E212 are scannable registered ECL drivers typically used as fan-out memory address drivers for ECL cache driving. In a VLSI array-based CPU design, use of the E212 allows the user to conserve array output cell functionality and also output pins.

The input shift register is designed with control logic which greatly facilitates its use in boundary scan applications.

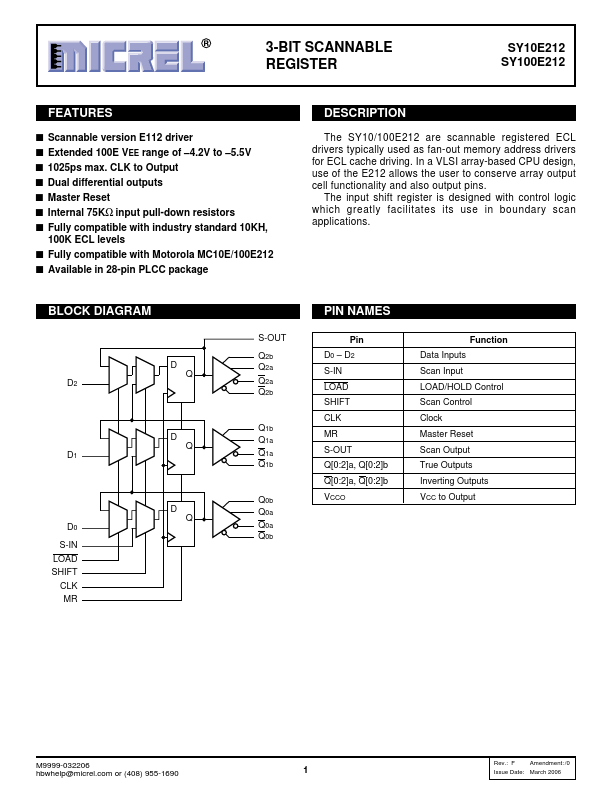

BLOCK DIAGRAM

D2

D1

D0

S-IN LOAD SHIFT

CLK MR

S-OUT Q2b Q2a Q2a Q2b

Q1b Q1a Q1a Q1b

Q0b Q0a Q0a Q0b

PIN NAMES

Pin D0

- D2 S-IN LOAD SHIFT CLK MR S-OUT Q[0:2]a, Q[0:2]b Q[0:2]a, Q[0:2]b VCCO

Function Data Inputs Scan Input LOAD/HOLD Control Scan...