PIC16F18075

Overview

The PIC16F180 microcontroller family has a suite of digital and analog peripherals that enable cost-sensitive sensor and real-time control applications. This product family is available from 8 to 44-pin packages in a memory range of 3.5 KB to 28 KB, with speeds up to 32 MHz.

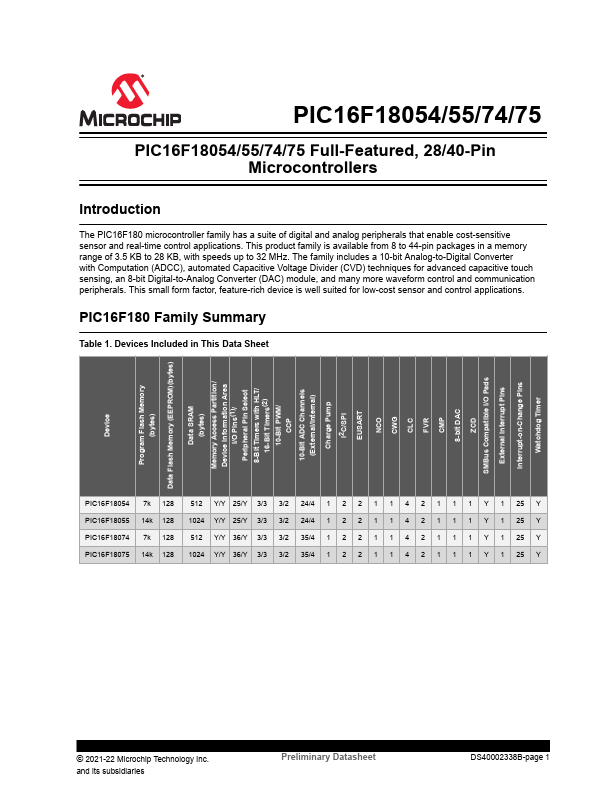

- Devices Included in This Data Sheet