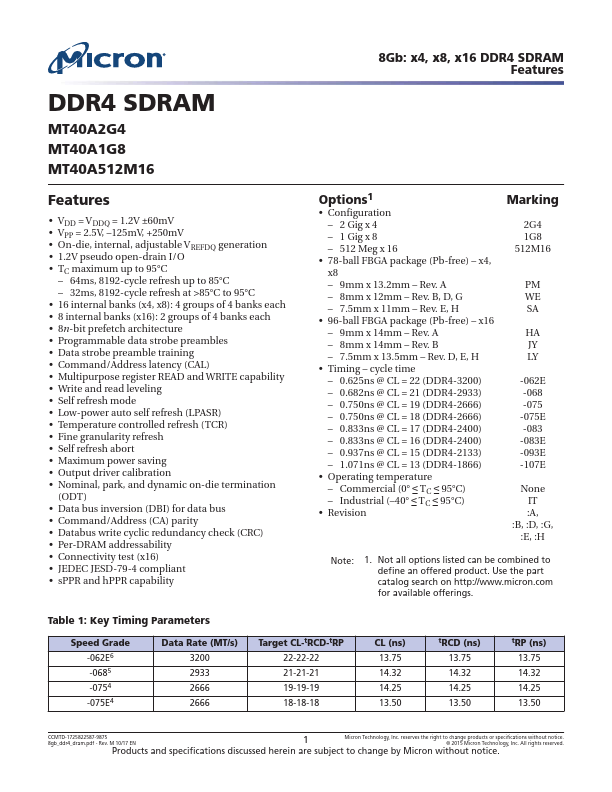

MT40A512M16

Features

DDR4 SDRAM

MT40A2G4 MT40A1G8 MT40A512M16

Features

- VDD = VDDQ = 1.2V ±60m V

- VPP = 2.5V,

- 125m V, +250m V

- On-die, internal, adjustable VREFDQ generation

- 1.2V pseudo open-drain I/O

- TC maximum up to 95°C

- 64ms, 8192-cycle refresh up to 85°C

- 32ms, 8192-cycle refresh at >85°C to 95°C

- 16 internal banks (x4, x8): 4 groups of 4 banks each

- 8 internal banks (x16): 2 groups of 4 banks each

- 8n-bit prefetch architecture

- Programmable data strobe preambles

- Data strobe preamble training

- mand/Address latency (CAL)

- Multipurpose register READ and WRITE capability

- Write and read leveling

- Self refresh mode

- Low-power auto self refresh (LPASR)

- Temperature controlled refresh (TCR)

- Fine granularity refresh

- Self refresh abort

- Maximum power saving

- Output driver calibration

- Nominal, park, and dynamic on-die termination (ODT)

- Data bus inversion (DBI) for data bus

-...