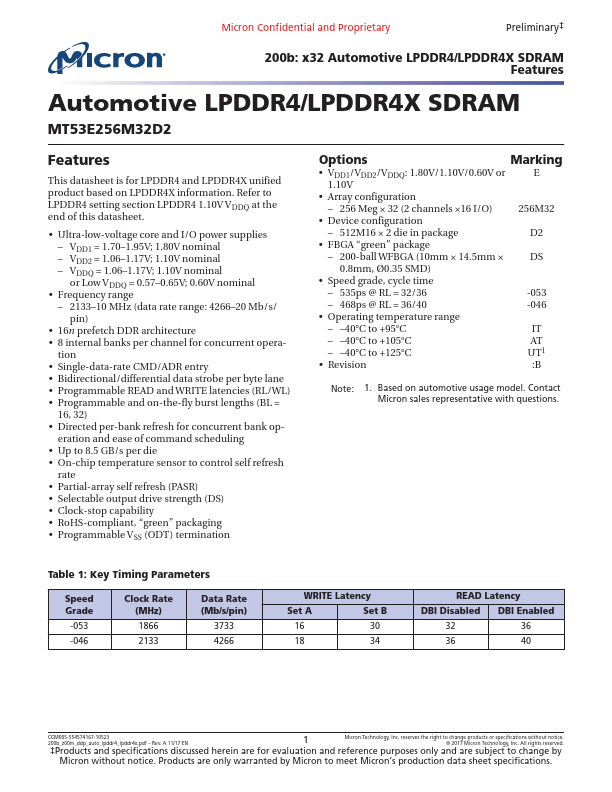

MT53E256M32D2

Features

Automotive LPDDR4/LPDDR4X SDRAM

Features

This datasheet is for LPDDR4 and LPDDR4X unified product based on LPDDR4X information. Refer to LPDDR4 setting section LPDDR4 1.10V VDDQ at the end of this datasheet.

- Ultra-low-voltage core and I/O power supplies

- VDD1 = 1.70- 1.95V; 1.80V nominal

- VDD2 = 1.06- 1.17V; 1.10V nominal

- VDDQ = 1.06- 1.17V; 1.10V nominal or Low VDDQ = 0.57- 0.65V; 0.60V nominal

- Frequency range

- 2133- 10 MHz (data rate range: 4266- 20 Mb/s/ pin)

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent opera- tion

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL =

16, 32)

- Directed per-bank refresh for concurrent bank op- eration and ease of mand scheduling

- Up to 8.5 GB/s per die

- On-chip temperature sensor to control self refresh rate

- Partial-array self refresh (PASR)

- Selectable...