74LS77

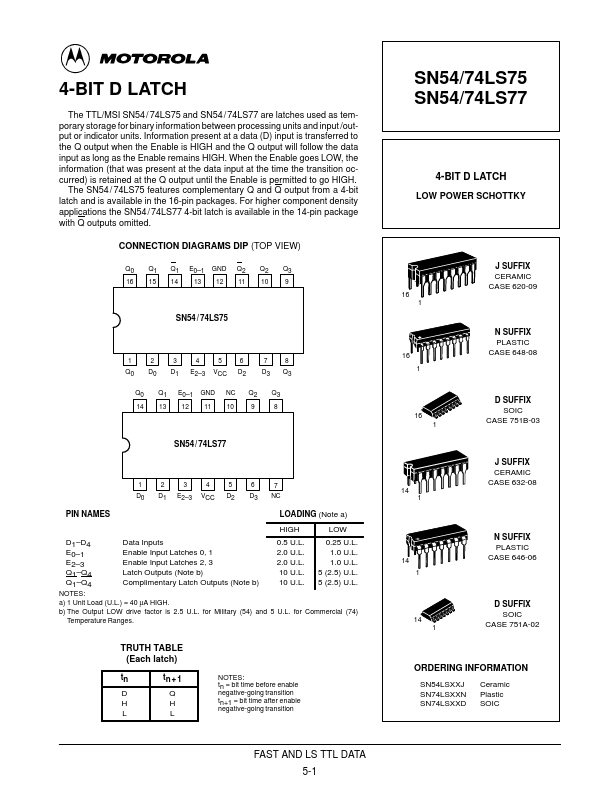

features plementary Q and Q output from a 4-bit latch and is available in the 16-pin packages. For higher ponent density applications the SN54 / 74LS77 4-bit latch is available in the 14-pin package with Q outputs omitted. CONNECTION DIAGRAMS DIP (TOP VIEW)

Q0 16 Q1 15 Q1 14 E0- 1 GND 13 12 Q2 11 Q2 10 Q3 9

SN54/74LS75 SN54/74LS77

4-BIT D LATCH

LOW POWER SCHOTTKY

J SUFFIX CERAMIC CASE 620-09

SN54 / 74LS75 N SUFFIX PLASTIC CASE 648-08

1 Q0 Q0 14

2 D0 Q1 13

3 D1

E2- 3 VCC NC 10

6 D2 Q2 9

7 D3 Q3 8

8 Q3

E0- 1 GND 12 11

16 1

D SUFFIX SOIC CASE 751B-03

SN54 / 74LS77 J SUFFIX CERAMIC CASE 632-08

14 1

1 D0 PIN NAMES

2 D1

3 E2- 3

4 VCC

5 D2

6 D3

7 NC LOADING (Note a) HIGH LOW 0.25 U.L. 1.0 U.L. 1.0 U.L. 5 (2.5) U.L. 5 (2.5) U.L.

D1- D4 E0- 1 E2- 3 Q1- Q4 Q1- Q4

Data Inputs Enable Input Latches 0, 1 Enable Input Latches 2, 3 Latch Outputs (Note b) plimentary Latch Outputs (Note b)

0.5 U.L. 2.0 U.L. 2.0 U.L. 10 U.L. 10 U.L.

14 1

N SUFFIX PLASTIC CASE...