MU9C4K64

Description

GENERAL DESCRIPTION

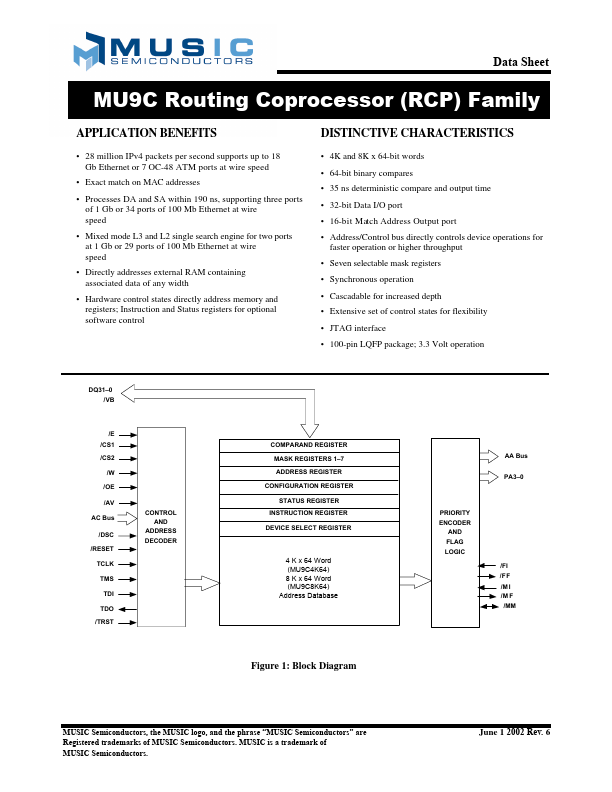

The MU9C RCP family consists of 4K and 8K x 64-bit Routing Coprocessors (RCPs) with a 32-bit wide data interface. The device is designed for use in layer 2 switches to provide very high throughput address translation using tables held in external RAM. The MU9C RCP has a fully deterministic search time, independent of the size of the list and the position of the data in the list. This unique feature guarantees that the wire speed address recognition does not impact the latency or induce some jitter on the latency of the global system. Address fields from the packet header are pared against a list of entries stored in the array. As a result of the parison, the MU9C RCP generates an index that is used to access an external RAM where port mapping data and other associated information is stored.

A set of control states provides a powerful and flexible control interface to the MU9C RCP. This control structure allows memory read and write, register read and...