Description

74HC3G04; 74HCT3G04

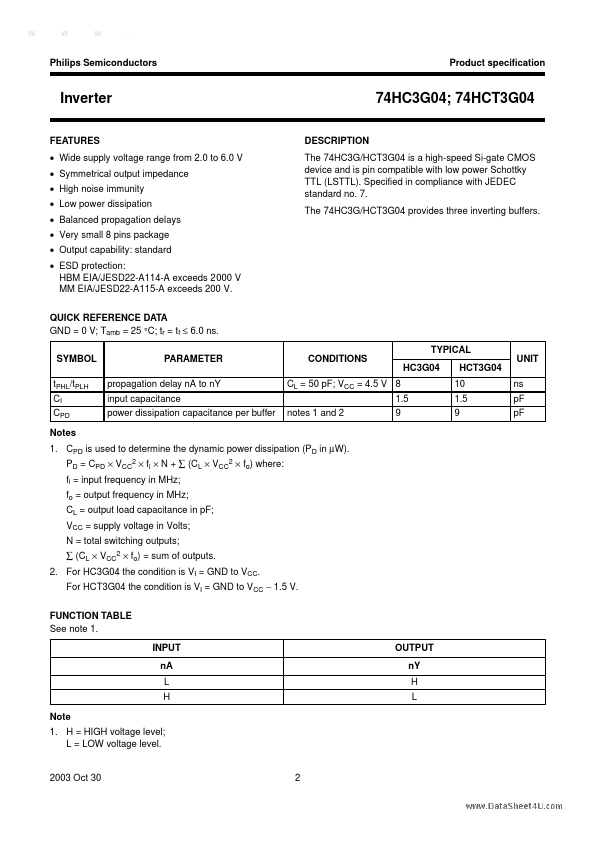

The 74HC3G/HCT3G04 is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL).Specified in compliance with JEDEC standard no.7. The 74HC3G/HCT3G04 provides three inverting buffers.TYPICAL SYMBOL tPHL/tPLH CI CPD Notes 1. CPD is used to determine the dynamic power dissipation (PD in µW).PD = CPD × VCC2 × fi × N + ∑ (CL × VCC2 × fo) where: fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VCC

Features

- Wide supply voltage range from 2.0 to 6.0 V.

- Symmetrical output impedance.

- High noise immunity.

- Low power dissipation.

- Balanced propagation delays.

- Very small 8 pins package.

- Output capability: standard.

- ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V MM EIA/JESD22-A115-A exceeds 200 V. QUICK.